# Hotplug in a Multikernel Operating System

Submitted by: Animesh Trivedi

August 19, 2009

Under supervison of Adrian Schüpbach, Dr. Andrew Baumann and Prof. Timothy Roscoe

Systems Research Group Department of Computer Science (D-INF) Swiss Federal Institute of Technology, Zürich (ETHZ)

### Abstract

The future manycore architectures present serious challenges to operating system designers. The traditional operating system designs can no longer manage the capabilities and power of the diverse heterogeneous cores with complex memory hierarchies, interconnects resembling networks, and distributed I/O configurations. The Barrelfish multikernel operating system addresses these issues by treating hardware as a distributed system. Cooperation in such an environment is achieved by message passing. We borrow similar design ideas in this thesis and present a distributed USB hot plugging infrastructure for a multikernel Barrelfish operating system. We have divided the USB system into three primary modules with different responsibilities: Host controller driver, USB manager and client drivers. This modular design provides necessary isolation and flexibility required in manycore systems. It also provides freedom to schedule and, if required, migrate any module independently among the cores depending upon the system workload and the application requirements. These modules communicate by explicit message passing but a few frequently updated and performance critical data structures are shared using shared memory mechanism. In this thesis, we try to design, implement and evaluate this system on top of message services and abstractions provided by the Barrelfish operating system.

### Acknowledgments

I would like to thank my mentor Prof. Timothy Roscoe for giving me the opportunity to work in Systems research group at ETH, Zürich. Over the past two years his constant motivation and enthusiasm for research has always inspired me to do better.

I would like to thank Dr. Andrew Baumann for his guidance and help while developing the work presented in the thesis. I have learned a lot from him during the course of our interaction in past few years.

I would also like to thank Adrian Schüpbach for his constant support, motivation, and inputs that I had during this thesis. His prompt response to my problems and long debugging emails had definitely helped me getting out of some tricky situations.

In the end, I would like to thank people of D-INF at ETHZ who directly or indirectly have helped me to get at this point.

# Contents

| 1        | Intr              | oduction & Problem Statement                | 8                |

|----------|-------------------|---------------------------------------------|------------------|

| <b>2</b> |                   | ice Drivers                                 | 10               |

|          | 2.1               | Improving Reliability of Device Drivers     | 10               |

|          | 2.2               | By Better Design Choices                    | 10               |

|          | 2.3               | By Improving Reliability and Driver Restart | 12               |

|          | 2.4               | By Analysis and Verification                | 13               |

| 3        | Bar               | relfish                                     | 15               |

|          | 3.1               | Barrelfish and device drivers               | 16               |

|          | 3.2               | Service Servers & Flounder                  | 17               |

| <b>4</b> | USE               | B System Overview                           | 18               |

|          | 4.1               | Hot Plugging                                | 18               |

|          | 4.2               | USB System                                  | 18               |

|          | 4.3               | USB Hardware                                | 19               |

|          |                   | 4.3.1 USB Host Controller                   | 20               |

|          |                   | 4.3.2 USB Hubs                              | 20               |

|          |                   | 4.3.3 USB Devices                           | 21               |

|          | 4.4               | USB Software                                | 21               |

|          |                   | 4.4.1 USB Client Driver                     | 22               |

|          |                   | 4.4.2 USB Bus Driver                        | 22               |

|          |                   | 4.4.3 Host Controller Driver                | 22               |

|          | 4.5               | Communication over USB                      | 22               |

|          |                   | 4.5.1 Control Transfer                      | 23               |

|          |                   | 4.5.2 Bulk Transfer                         | 23               |

|          |                   | 4.5.3 Interrupt Transfer                    | 23               |

|          |                   | 4.5.4 Isochronous Transfer                  | 24               |

|          | 4.6               | Interaction with Devices                    | 24               |

| 5        | ĘЦ                | CI Overview                                 | <b>25</b>        |

| 0        | <b>EIV</b><br>5.1 | Registers and Mackerel Interfacing          | <b>⊿</b> 5<br>25 |

|          | $5.1 \\ 5.2$      | 0                                           | $\frac{25}{26}$  |

|          | 0.2               | Associated Data Structures                  | 20<br>27         |

|          |                   |                                             |                  |

|    |                | 5.2.2 Queue Heads (QHs) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 27$                       |

|----|----------------|-----------------------------------------------------------------------------------------------------|

|    | 5.3            | Operational Model                                                                                   |

|    |                | 5.3.1 Port Routing and Control                                                                      |

|    |                | 5.3.2 Periodic Queue                                                                                |

|    |                | 5.3.3 Asynchronous Queue Management                                                                 |

|    |                | 5.3.4 PING Protocol Maintenance                                                                     |

|    |                | 5.3.5 Data Toggle Synchronization                                                                   |

|    |                |                                                                                                     |

| 6  | $\mathbf{Dis}$ | tributed USB Infrastructure 33                                                                      |

|    | 6.1            | Overview                                                                                            |

|    | 6.2            | Communication Between the Domains                                                                   |

|    | 6.3            | Proxy Function Implementations                                                                      |

|    | 6.4            | Synchronization                                                                                     |

|    | 6.5            | Hot-plugging 36                                                                                     |

| 7  | TICI           | B Memory Management 37                                                                              |

| 1  |                | 2 0                                                                                                 |

|    | 7.1            | Internal Memory Management                                                                          |

|    | 7.2            | NUMA Aware I/O Buffer Allocation                                                                    |

|    | 7.3            | Library Interface and Functions                                                                     |

| 8  | Hos            | st Controller Driver (HCD) 43                                                                       |

|    | 8.1            | PCI Interfacing and Booting the Host Controller 43                                                  |

|    | 8.2            | Event Notifications                                                                                 |

|    | 8.3            | Device Detection and Port Power                                                                     |

|    | 8.4            | Asynchronous Queue Management                                                                       |

|    | 8.5            | Transaction Management 47                                                                           |

|    | 8.6            | Host Controller Server's Services                                                                   |

| •  | TIO            |                                                                                                     |

| 9  |                | B Manager 51                                                                                        |

|    | 9.1            | Device Plug & Unplug                                                                                |

|    | 9.2            | Device Enumeration                                                                                  |

|    | 9.3            | USB Tree Topology                                                                                   |

|    | 9.4            | Communication                                                                                       |

|    |                | 9.4.1 With HCD 55                                                                                   |

|    |                | 9.4.2 With Client Driver $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 55$ |

|    |                | 9.4.3 With SKB                                                                                      |

|    | 9.5            | USB Manager Server's Services                                                                       |

|    |                | 9.5.1 To HCD                                                                                        |

|    |                | 9.5.2 To Client Driver $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 57$          |

| 10 | TICI           | P Davias Drivers                                                                                    |

| 10 |                | B Device Drivers 59                                                                                 |

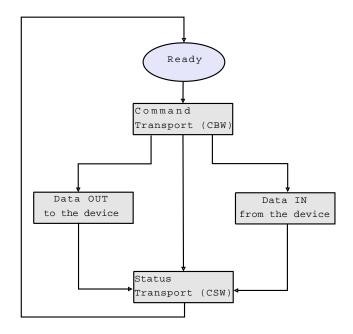

|    | 10.1           | Mass Storage Protocol Specification                                                                 |

|    |                | 10.1.1 Command Block Wrapper (CBW)                                                                  |

|    |                | 10.1.2 Status Block Wrapper (CBW) $\ldots \ldots \ldots \ldots \ldots 62$                           |

|    |                |                                                                                                     |

| 10.2 Mass Storage Class Driver   | 63 |

|----------------------------------|----|

| 10.2.1 Implemented SCSI Commands | 64 |

| 10.3 Driver Server's Services    | 66 |

| 11 Evaluation                    | 69 |

| 12 Conclusions                   | 75 |

| 13 Future Works                  | 76 |

| Bibliography                     | 77 |

# List of Figures

| $4.1 \\ 4.2$                              | USB connection topology                                                                                                                    | 19<br>20                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| $5.1 \\ 5.2 \\ 5.3$                       | qTD data block layout                                                                                                                      | 27<br>28<br>30             |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Distributed USB infrastructure                                                                                                             | $\frac{34}{35}$            |

| 7.1                                       | USB Memory Management                                                                                                                      | 39                         |

| 8.1                                       | HCD asynchronous queue management overview                                                                                                 | 46                         |

| 9.1<br>9.2                                | Configuration descriptor with interface and endpoint descrip-<br>tors                                                                      | $52\\54$                   |

| -                                         | Command/Data/Status Flow                                                                                                                   | 54<br>61                   |

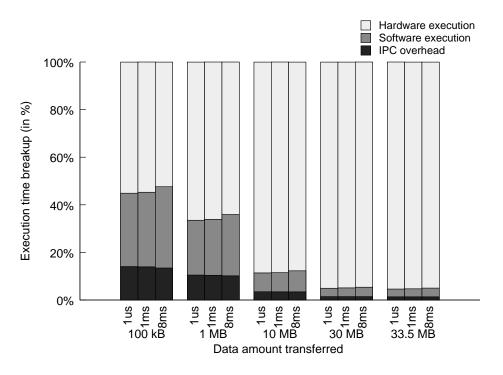

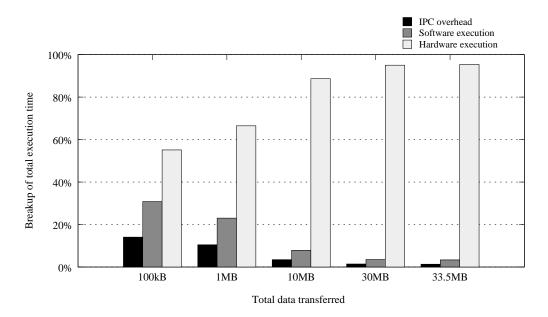

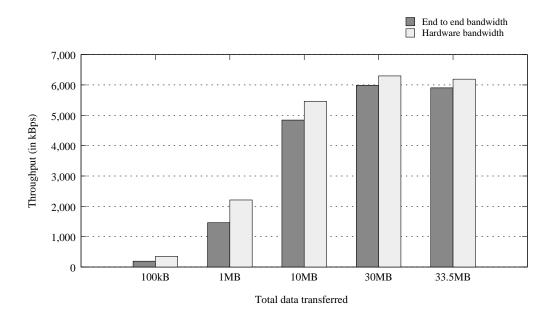

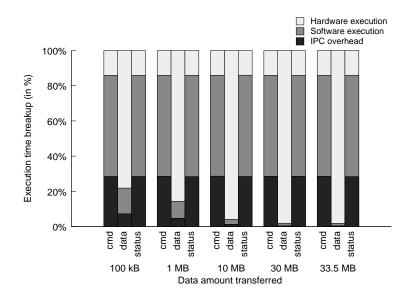

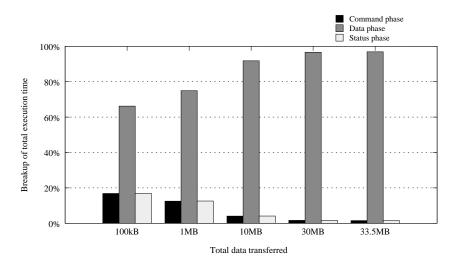

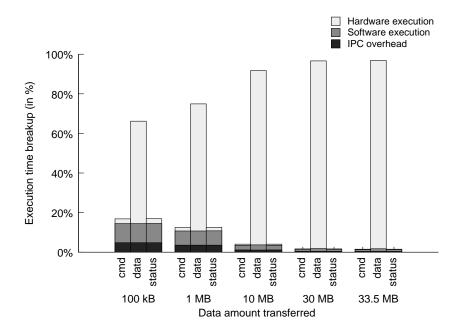

| $11.1 \\ 11.2 \\ 11.3 \\ 11.4 \\ 11.5$    | Execution time breakup $\dots \dots \dots$ | 69<br>70<br>71<br>72<br>72 |

|                                           | spent in each stage                                                                                                                        | 73                         |

# List of Tables

| 5.1  | EHCI capability registers           | 26 |

|------|-------------------------------------|----|

| 5.2  | EHCI operational registers          | 26 |

| 10.1 | Bulk-Only data interface descriptor | 60 |

| 10.2 | Command block wrapper               | 61 |

| 10.3 | Status block wrapper                | 62 |

| 10.4 | Valid command block status values   | 63 |

| 10.5 | Valid device qualifiers             | 65 |

|      |                                     |    |

### Chapter 1

# Introduction & Problem Statement

Hardware landscape has changed tremendously over the past decade. Intel is envisioning 'Tera-scale' computing [1] and AMD is making heterogeneous chips by putting GPU and CPU in a same package [2]. Things have moved from a single fast processor to the heterogeneous manycore architectures; from a flat uniform access memory to the non-uniform memory access; from a centralized device management to the distributed device management. With hardware getting more diverse, a system starts to resemble like a network and factors such as quality of service in system interconnect, congestion, hop counts, delays, hot plugging (akin to node joining or failure), rapid prototyping and testing are getting more important. This hardware diversity has three major aspects [3]:

- Non-uniformity: Apart from the much discussed non uniform memory access (NUMA) architectures, multiple level of cache sharing is also common in manycore processors. Hence a flat uniform shared memory model may not be the best way to model this complex memory hierarchy. Additionally the actual cost of accessing memory depends depends upon interconnect topologies like Hypertransport and Quickpath, and factors such as hop count and routing play an important role.

- **Core diversity:** In near future the processing core will be much more diverse and heterogeneous. The system will have more number of specialized cores with different performance, power trade offs and possibly different instruction sets.

- **System diversity:** With the internal system components getting diverse, it will be difficult to write and optimize system software about any specific target. With a network like interconnect topology the access to devices in the system also depends on which core driver code is

running. Even today, AMD systems have two PCI root complex and cores near root complex have faster access to the devices than other cores sitting on the other side of the bus.

Barrelfish [4] is a new operating system, designed specifically for handling future manycore heterogeneous architectures. It is a multikernel operating system, which treats computer hardware as a distributed system where a node represents an entity inside the computer box such as CPU, devices, GPU etc. Nodes communicate much like as done in a distributed environment by passing messages on previously agreed protocols.

Handling dynamic plugging and unplugging of devices in such a distributed environment imposes some interesting challenges such as where to run code for the drivers, how to manage workloads, how to reflect status of the devices to the rest of system etc. Modularity in a big system like USB is an important issue. With three different kinds of controllers and plenty of devices around it is desired to have a clean design which is flexible and can provide necessary isolation and protection. With system internals getting much more diverse it is also important to think about abstraction provide to the higher layers.

In this thesis we present USB hot-plugging infrastructure for Barrelfish operating system. The thesis is organized as follow. Chapter 2 gives an overview of related device driver research work. Chapter 3 introduces and talks about Barrelfish operating system and its interaction with device drivers. Chapter 4 and 5 give an overview about USB protocol and Intel EHCI controller hardware. In chapter 6 we introduce our distributed USB infrastructure. Chapter 7, 8, and 9 talk in detail about USB memory management, host controller driver and USB manager respectively. In chapter 10 we will provide a brief overview of the USB mass storage protocol and details about our implementation of the device driver for flash mass storage device. Chapter 11 gives detail about evaluation and performance. In the chapter 12 we present some conclusions and we end in chapter 13 after giving some directions about the future work.

### Chapter 2

## **Device** Drivers

Device driver is a piece of software which allows operating system kernel and other higher level programs to interact with a hardware device. Device drivers make up majority of operating system's code base, which requires support for myriad of devices. Also, these are the most buggy and unreliable part of an operating system code. In Windows XP, drivers cause 85% of reported failures [5]. Padioleau et al. [6] gives a comprehensive overview of driver evolution in the Linux kernel.

#### 2.1 Improving Reliability of Device Drivers

Device drivers have drawn considerable amount of attention from systems research community to improve reliability of commodity operating systems. These efforts can be break down into following sections depending upon their level of application:

#### 2.2 By Better Design Choices

In a traditional operating system model, device drivers are run into kernel space. Hence a faulty driver can corrupt internal kernel data structures and can bring whole system down. To cope up with such situations kernel designers have advocated moving drivers out into the user space from kernel space and to facilitate communication through inter process communication (IPC) primitives [7, 8]. Often due to an inefficient implementation, this design exhibits poor performance [9]. Though [10] has shown to achieve good performance with the user space driver designs. This approach can not be applied to already deployed legacy driver code base which would require a complete rewrite.

Driver virtualization helps in isolating the buggy device drivers from rest of the systems and hence improves its stability. In driver virtualization device drivers (often unmodified or with little engineering efforts) are run in separate isolated virtual machines [11, 12]. It provides better driver re-usability with strong isolation. At the same time it invokes trust issues between the kernel and virtual machines. Also drivers operating in different virtual machines raise timing and lock synchronization discrepancies. Addendum, poor performance in such systems (specially in server workloads) can [13] be a limiting factor in their deployment. Twindriver [14] approach tries to address this issue by semi-automatically deriving hypervisor drivers from guest OS drivers. It runs performance critical operations directly into the hypervisor and coordinates with the guest OS instance of the driver. It uses Software Virtual Memory (SVM) mechanism to let hypervisor instance efficiently access the driver data in guest OS address space while protecting hypervisor address space from corrupted memory access from guest OS driver.

Chipounov et al. [15] tries to reverse engineer a driver for better reliability and reasoning, by monitoring the interaction between a device and the driver. It combines these traces with static analysis of the driver to derive a protocol state machine. This machine is then used to synthesize new drivers from pre-verified safe driver templates. New drivers are safe by virtue of construction because only *safe* set of traced data was used to extract the protocol.

Microdriver approach [16] offers a trade off between an in-kernel driver's performance and an user level driver's isolation. It factors a driver into two parts: a performance critical part and another non-critical part. Performance critical code is then moved to the kernel space and non-critical code is run in user space. I/O data transfer logic, which often resides in performance critical code paths, is moved into kernel space. Non-critical path usually contains device management and configuration, error handling etc. Both instances communicate and synchronize to complete a request. User mode driver helps in driver isolation and error containment. Also driver developers can get a helpful support from the traditional developing, testing and debugging tools and libraries, which often are absent when developing in-kernel drivers. To automatically split driver code into kernel and user space driver, Microdriver requires manual annotations from developers to properly identify the shared data structures.

#### 2.3 By Improving Reliability and Driver Restart

To address the issue of in-kernel data corruption, Nooks [5] provides a inkernel subsystem that helps in preventing such errors. Nooks executes inkernel extensions such as device drivers and loadable file-system modules etc. in an isolated lightweighted kernel protection domain. The domain still is in kernel mode but with a restricted write access to the critical in-kernel data structures. A new reliability layer keeps tracks of all the modifications made by an extension and traps any unwanted changes, such as invalid arguments for a kernel service or consumption of too many resources in the system. Upon error detection or failure, recovery logic is triggered. Nooks was able to detect and isolate 99% of errors injected in a testing Linux system. Though Nooks is not able to differentiate between a faulty and a malicious driver. A driver (malicious) still can corrupt system state by executing privileged instructions. It provides very basic kind of recovery mechanism by securely freeing all allocated resources to the failed driver and then restarting it. It relies on virtual memory hardware support for isolation within kernel. Also, it does not support any user level tools during development of a driver which could have been helpful in detecting basic control flow errors such as infinite loops etc.

Much of the effort in the direction of reliable operating systems has been put to make OS kernel immune to a faulty in-kernel driver. In such systems if a driver crashes, then kernel survives but not the driver applications. From an application's perspective either both, kernel and driver, should work or none. Having a surviving lone kernel is not much of a use to an application, which lost data in driver failure. Shadow driver [17] provides an elegant way to transparently restart the driver. It inserts a shadow driver *tap* between kernel and the driver, and passively monitors all the communication between these two. Upon detection of a failure, it actively replaces the failed driver with a shadow driver and triggers the restarting mechanism. Shadow driver is not a true driver as it does not provide complete driver services but it is used to hide driver failure from applications by impersonating the communication between applications and the driver. Once failed driver has been restarted shadow driver delegates the pending requests and control over to it. Shadow driver uses kernel support for dynamic loading and unloading of drivers as its primary mechanism to restart a failed driver. It assumes failed driver subsystem has no side effects. This assumption may be not true for stacked drivers. A failed EHCI controller or a PCI driver can cause failure to many other driver systems in a cascading effect. It also may have limited applicability because it requires explicit communication among driver, applications and kernel for tapping. It is not possible to deploy it for the class of drivers which use shared memory mechanism for communication such as video drivers etc. Also due to timing discrepancies it is ill-suited for applications with real time demands.

XFI [18] suggests a software guard for protection of system address space but suffers from poor performance and lacks control flow safety checks.

#### 2.4 By Analysis and Verification

Many researchers argue to use a type safe language for driver or kernel extension development. But because of the high overhead and less control these solutions are less appealing to the driver development communities. SafeDrive [19] provides a way to do type checking on existing systems which are coded in C. It uses annotations in C to define semantics and does fine grained memory safety checking. Pointers and no-annotation in legacy code can be problematic for its deployment. To overcome these limitations [20] proposes the use of a *Secure Virtual Architecture* (SVA), which performs run time monitoring and checks based on LLVM.

[21] uses the same technique as of Microkernel architecture by moving device drivers into the user space but it goes one step further by validating their references. It uses device safety specification (DSS), which describes state and transition of driver state machine. All the references from the driver including memory, I/O ports, interrupts, registers etc. are validated through reference validation mechanism (RVM). If a driver is caught attempting to execute an illegal operation, it then is stopped and restarted. Though approach sounds promising but defining and clear state machine for complex devices may require considerable amount of efforts. Also doing *unsafe* driver restart is not desirable in high availability systems.

Due to frantic pace at which modern devices are being developed it is hard to catch up with them. To improve reliability of hardware operating code for devices Devil [22] attempts to check and verify device register manipulations before actually writing them to devices. Devil is an interface definition language (IDL) which upon giving device communication interface and related semantic specifications, generates safe hardware operating code to operate the device. Devil lacks, run time assembly checks, bus architecture and communication protocol considerations (like PCIe and USB, packet passing in USB), new features such as power management etc. Ryzhyk et al. [23] proposes to formalize the communication interface between device driver and an operating system kernel. Their solution is based on a formal state machine based verification, which helps in enforcing correct driver behavior. It requires a major rewrite of device drivers and extracting state machine information from device specification could be an error prone task. Similarly, Dolev et al. [24] have also proposed a notion and requirements for a self stabilizing device drivers based on a state machine approach.

Ball et al. [25] proposes to perform a comprehensive static analysis of the device drivers. They emphasize on proper kernel API usage. Their static driver verifier (SDV) tool uses a static analysis engine (SLAM) with *API usage rules* to find kernel API abuses. It reduces the program control flow into a boolean program abstraction which preserves control flow of the C code. Then system performs symbolic model checking to ensure that the program obeys the API usage rules. It is quite useful to find many programming glitches before actual deployment of the driver. On the other hand it completely ignores the driver behavior and implementation related bugs and focuses only on API usage aspect of it. Due to close integration with operating system (in this case, Windows platform) and its API documentation, it would require significant efforts to port it to other systems. DDVerify [26] attempts to port technique introduced by it to Linux with further enhancements such as verifying concurrent software with shared memory.

As a pure language based solution, Spear et al. [27] proposed a design to verify and reason about the correctness of a device driver. Drivers are written in a type safe language. To prevent corruption to system state, drivers are run in user space. Hardware resources are only accessed through messages, and when granted access from the verification system. Verification system relies on meta-data resource declarations for carrying out assessment of a request. It relies on the type safe language capabilities to restrict malicious behavior of a driver code.

# Chapter 3

### Barrelfish

The system hardware is changing at a much faster pace than before. The execution cores are getting heterogeneous in terms of power requirements, instruction sets, speed, and capabilities. The flat uniform memory assumption on which traditional operating system designs are built is no longer valid. Barrelfish aims to manage and exploit power and capability of such future manycores system.

Barrelfish [4] is a multikernel operating system. The kernel design is inspired by the microkernel design architecture [7, 9]. The Barrelfish kernel only runs a set of minimal services which are required to run in privileged mode such as scheduler, message sending services etc. All other responsibilities are managed by special user space service servers like memory manager, file system manager etc. By lowering the foot print of the kernel one can also argue about correctness and reliability of the system. The system design is built around three design principle. First, make all intercore communication explicit. It removes OS design reliance on the shared memory model, which is a bottleneck point in the system. It also improves overall understanding of the system as now operating system knows *what*, *when* and *who* about system state updates.

Second, have minimum OS design dependency on hardware. The only architecture specific code in Barrelfish is message transport mechanism and interface to hardware (CPU and device drivers). Hence the higher layer protocols and algorithms are isolated from the low level hardware details.

Third and the last, replicate instead of share. Many system states like dispatcher queues are shared among processors to get a consistent view of the system. These shared data structures act as contention points and restrict system scalability. To counter this issue Barrelfish replicate system state between core instead of sharing. Consistency is maintained by message passing.

#### 3.1 Barrelfish and device drivers

Like in any other operating system (OS) device drivers are responsible for handling devices in Barrelfish. This new 'distributed' environment presents many interesting challenges for driver developers as well as to the OS in terms of efficient and optimized resource usage. As shown and discussed in [3], in a system with network like interconnect (AMD NUMA machines) the cost of accessing a device and memory depends upon on which core the driver is running. The difference is significant in terms of memory access. Hence it is *desirable* to do a topology aware resource allocation for the drivers for better resource usage and performance. Drivers which run on cores which have direct access to device and associated data buffers in memory are expected to perform well in such systems. As shown by [4], with changes in spatial configuration of network card, driver and memory buffers, the UDP goodput was decreased from 887.9 Mbps to 502.7 Mbps.

To manage complexity of modern systems, Barrelfish makes use of a *system*  $knowledge \ base \ (SKB)$ . It contains representation and information about machine's hardware and current state. It can be queried by other services in system to get knowledge about:

- 1. Resource discovery, such as a new USB device is attached.

- 2. Online measurement and profiling, for things like available bandwidth, latency or power on USB. It may be probed to check if with current configuration USB system is able to satisfy requirements of a newly connected device.

- 3. A priory knowledge about a device or controller, from data sheets [28].

Such queries *can* answer about the appearance and disappearance of devices, their capabilities and requirements etc. Hence pushing conventional driver architecture towards declarative systems. Declarative systems are more reliable and one can reason about their correctness unlikely as in imperative systems. Also it helps in topology aware device management logic. For example, a USB device can put it requirements in terms of polling frequency, delay threshold, bandwidth etc and then controller after consulting SKB about current tree topology can assert whether it will be able to full fill these requirements or not. Similarly, it could provide suggestions about device relocation (like in systems with multiple USB ports), whenever possible, for better performance.

In Barrelfish, device drivers are run as user level processes in their own separate execution domain. Hence a buggy driver can not crash down whole operating system. Device access is done by memory mappings. OS services are provided by the *service servers* like PCIe server and clients communicate with them by message passing. In such a distributed environment, USB driver *should* be developed as a distributed driver with different functionality such as configuration, device management, data transfer etc. running on different cores. To make a better match with current system state and driver requirements one can factor a driver in performance critical and non-critical segments similarly to the Microdriver architecture [16]. Performance critical piece of code can be deployed on cores near to the device. Driver also can specify their requirements (much like in [27]) prior to their initialization so that an appropriate core can be selected. I/O buffers (and their management logic) which often are in performance critical paths can be allocated in RAM of cores which are nearer to the device. Other things like configuration management, error recovery etc. which are executed occasionally can be run on other under utilized cores. A periodic evaluation system, which upon a requirement or request can relocate these pieces to different cores, if approved by underlying decision making architecture.

#### **3.2** Service Servers & Flounder

Like in a distributed environment the services in Barrelfish are provided by service servers. Anything from frame allocation, memory mapping, interrupt delivery, device discovery etc. are provided by specific servers. The requests are send and response is received by explicit message passing. Example of few service servers are memory server, PCI server, EHCI controller server, SKB server etc.

Barrelfish maintains a name-server called *Chips* which is a centralized name server registry. A new server has to register its services and name to the Chips. All message passing are done on names of servers. Server clients can search specific server name using SKB, if appropriate entries are made into it.

Since message passing mechanism is vital and used intensively in Barrelfish, a domain specific language (DSL) *Flounder* is developed for hiding these explicit message passing mechanisms. Flounder takes the service interface specifications and automatically generates associated server and clients stubs. These stubs help in communicating with Chips for service registration, message passing between server and clients, registering service handlers, and invoking the handler when an associated message is received. More details can be found in Flounder manual [29] at Systems Research Group, ETH.

### Chapter 4

### **USB** System Overview

This chapter gives a brief overview of Universal Serial Bus (USB) 2.0 protocol. It also talks about key elements in USB architecture and how data is moved across the USB bus. For complete reference please refer to the official USB documentation [30]. The chapter highlights the related sections in the documentation for cross reference purposes.

#### 4.1 Hot Plugging

Hot plugging or Hot swapping is a technology which enables user to replace, remove or add system components to a running system without shutting it down. Once the appropriate software/driver is installed on the system, user can plug and play the attached peripheral without rebooting the system. Hot plugging is a desirable property in the systems with high availability. It enables the system maintainer to remove faulty component or add additional peripherals for redundancy without affecting the running system. Hot plugging examples include, a faulty RAID disk can be replaced by a new one with using hot plugging, USB mass storage devices, USB wireless cards etc.

#### 4.2 USB System

The universal serial bus (USB) is a complex bus design to connect a host computer to a number of different peripheral devices. It aims to replace various wide range and slow buses like parallel, serial etc. with a standard bus which can be used to connect variety of devices such as keyboards, mouse, printer, web cam, storage devices etc. The latest revision of USB is 2.0 (High speed) which supports bandwidth up to 480 Mbps (or 60 MBps) and 127 devices per host controller. The next revision, 3.0 is under development and expected to support bandwidth in the range of 5 Gbps [31].

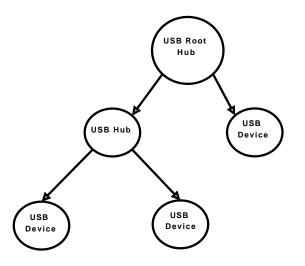

Figure 4.1: USB connection topology

The design goals of USB system include:

- A single connector to connect any PC peripheral

- A method of avoiding system resource conflicts

- Hot plug support

- Automatic detection and configuration of the USB devices

- Low cost

- Enhanced performance capabilities

- Support for legacy devices

- Low power consumption

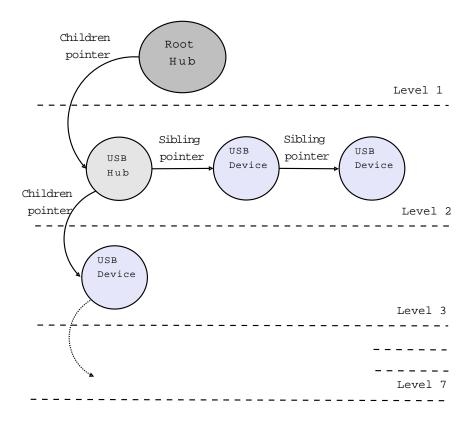

A typical USB system consists of a host controller, hubs and devices. USB bus topology is laid out as a tree. Host controller acts as the root and others, hubs and devices, act as internal and leaf nodes respectively, which are connected through several point to point links. Hubs can be seen as expansion slots which helps in expanding the USB tree as shown in figure 4.1. The hub uses a master-slave protocol for communicating with the devices. Hence every kind of communication (in or out) is initiated by the host controller. By choosing the master-slave protocol USB does not have to do a distributed bus arbitration to avoid collision on the shared resource.

#### 4.3 USB Hardware

The USB hardware present the part which is actually implemented in the silicon. A complete USB system has three major hardware components:

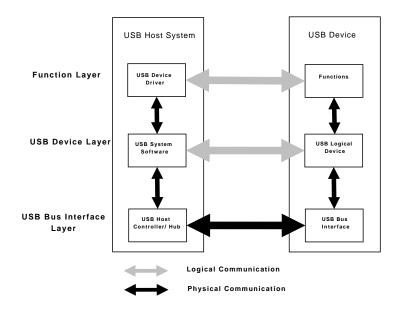

Figure 4.2: Communication flow in a USB system

#### 4.3.1 USB Host Controller

The host system hardware contains a USB host controller which is responsible for initiating the transaction over the USB system under host driver control. The three generations of controllers have been around which are:

- 1. Universal host controller interface (UHCI) (USB 1.0)

- 2. Open host controller interface (OHCI) (USB 1.1)

- 3. Enhanced host controller interface (EHCI) (USB 2.0)

The host controller reads the list of USB transactions and executes them. If a write to a device has been requested then controller will read data from buffer supplied from USB client driver and deliver it to device. In case of read, when device sends data back to host controller, it forwards it to buffer supplied by USB client driver.

#### 4.3.2 USB Hubs

USB hubs are like attachment points for the USB system where user can insert a device or even another hub. They are responsible for enabling/disabling the ports, maintain status of ports and notifying the host controller in case of events such as attachment/removal of device happens on the port. Every USB host contains a root hub which is a central attachment point and all USB traffic originates from it.

#### 4.3.3 USB Devices

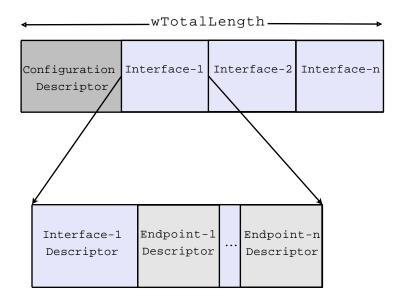

USB devices are special devices which can understand USB protocol. Any device functionality can be ported to USB protocol given bandwidth, delay requirements etc. are met. They are powered and configured after plugging into the system by the USB driver. Every USB device has a *device descrip*tor which is presented to host controller at the time of configuration. It contains information regarding features and capabilities required to operate the device and help finding corresponding client driver for it. An USB device can be a low (1.x), full (1.x) or high (2.0) - speed device. An USB device has only one device descriptor but can have multiple configuration descriptors corresponding to device's power or bandwidth requirements. Going further, a configuration descriptor can have multiple *interface descriptors*, which themselves can have multiple *endpoint descriptors*. A single USB device can present itself as more than one device having different interfaces e.g. a web cam with a microphone or speakers, connected through a single USB connection to host system. Such USB device will require different client drivers depending upon which interfaces have been enabled on the device.

An endpoint acts like a data source or sink. The endpoint descriptor provides information related to endpoint's transfer type, direction (IN or OUT) and data rate supported. A pipe is a logical entity that connects endpoint to the client driver. Pipe can be of two type:

- Message pipe: Content which is delivered through message pipe is required to have standard USB defined structure. Transfer on message pipe is done in a three step process, consists of a request, optional data and status phases. Message pipes allow communication in both direction. Default control pipe, which is used to configure devices, is always a message pipe.

- **Stream pipe:** Stream pipes deliver data with no USB required structure on data content. Stream pipes are always unidirectional in content flow. Stream pipes support bulk, isochronous and interrupt transfer types.

Section 5.3.2 in USB documentation discusses in detail about pipes and their types.

#### 4.4 USB Software

The USB software system consists of following three layers:

#### 4.4.1 USB Client Driver

USB client or device driver is the highest layer in the software hierarchy. It is responsible for implementing a typical device functionality such as keyboard, mouse, web cam, USB mass storage etc. and often is unaware of underlying complexity of USB architecture. It issues I/O requests to USB bus driver in terms of I/O Request Packets (IRPs).

#### 4.4.2 USB Bus Driver

The USB bus driver understands the USB bus topology and target device characteristics. It also keeps track of device bandwidth and power requirements. When an IRP is received from USB client driver, it breaks the request into USB transactions which will be executed on the next frame. A frame is a bus time quanta on which different transactions are scheduled. A typical USB 1.x frame is 1 ms and corresponding USB 2.0 frame (often called *microframe*) is 125  $\mu$ sec.

- A USB bus driver is responsible for:

- Device configuration management

- Data transfer management

- Bus management

#### 4.4.3 Host Controller Driver

The host controller driver (HCD) is primarily responsible for scheduling the USB transactions over the bus. HCD maintains lists of various pending transactions (control, bulk, interrupt or isochronous)<sup>1</sup> and schedule them accordingly. The specifications of scheduler is implementation dependent. According to Intel EHCI documentation [32], system software maintains two schedule for the host controller: a periodic schedule and an asynchronous schedule. The isochronous and interrupt USB transactions fall into the periodic schedule, while bulk and control transfers belong to the asynchronous list. In each microframe if periodic schedule is enabled then host controller will execute from the periodic list. It will only execute from the asynchronous schedule after it reaches the end of periodic schedule. Chapter 5 discuss in detail about EHCI hardware.

#### 4.5 Communication over USB

An USB device client initiate a transfer when it puts I/O requests in terms of IRPs to USB bus driver. The client driver supplies a buffer required to

<sup>&</sup>lt;sup>1</sup>explained in next section

hold or provide data for the transfer. The bus driver breaks the IRPs into small USB transactions which adhere to the bus and protocol requirements. A transfer happens between a client driver and an endpoint on the USB device. USB supports following types of transactions over an endpoint:

#### 4.5.1 Control Transfer

It is used to send and request short data packets to configure an USB device. It involved reading and setting device, configuration, interface and endpoint descriptors.

A control transfer is consists of a *setup* bus transaction moving standard request information from the host to a device, zero or more *data* transactions sending data in the direction indicated by the setup transaction and a *status* transaction returning status information from a device to the host. A setup transaction is only considered complete if status returned shows "success".

Control transfer is done on messages pipes by sending standard USB commands codes. The data exchanged on message pipe also has USB defined structure. The section 5.5 in USB documentation discuss in detail about control transfers.

#### 4.5.2 Bulk Transfer

It is used to send and request relatively large amount of data packets using maximum allowable bus bandwidth. Modern USB storage devices use this transfer type. Requesting a pipe with a bulk transfer type provides the requester with:

- Access to USB on a bandwidth-available basis.

- Reliable delivery.

- Guaranteed delivery but no guarantee for bandwidth or latency.

USB imposes no data content restriction on transferred data. Bulk transfer employs stream pipes hence are uni-directional. The section 5.8 gives more detail about bulk transfers on USB.

#### 4.5.3 Interrupt Transfer

Interrupt transfer is used with those devices which need to send or receive data infrequently but with a bounded service periods. Host controller will automatically repeat these type of requests in the specified time intervals. It provides:

• Guaranteed maximum service period for the pipe.

• Retry of transfer attempt on next period in case of a failure.

It uses stream pipes and has unidirectional traffic. Section 5.7 in USB 2.0 documentation gives more comprehensive overview about it.

#### 4.5.4 Isochronous Transfer

It is used to send or receive real time data streams with guaranteed bus bandwidth but without any reliability. These are suitable for A/V devices and signals. The traffic through these pipes is constant-rate and error tolerant. It provides:

- Guaranteed access to USB bandwidth with bounded latency.

- Guaranteed constant rate data though pipe as long as data is provided to the pipe.

- No retries on occasional failures.

Isochronous transfer uses stream pipes and is unidirectional. Section 5.6 in USB 2.0 documentation gives more details about it.

#### 4.6 Interaction with Devices

The USB devices operate on two separate layers. The layer one can be seen as *control layer* which is responsible for maintaining the device status, processing control requests, setting up configuration and interface. The second layer is *functionality layer*. This is the actual functional capability that the device provides like a mouse, or flash storage etc.

The communication to control layer is done though message pipes and with set of standard commands which are explained in section 9.3 and 9.4 of USB 2.0 documentation. The response for these commands are also standard descriptors (device, configuration, interface or endpoint). These are explained in section 9.5 of USB 2.0 documentation.

Chapter 9 of USB documentation gives comprehensive details of USB devices framework and associated descriptors.

### Chapter 5

### **EHCI Overview**

Enhanced host controller interface (EHCI) is an USB host controller (HC) hardware specification for USB 2.0 protocol. In this chapter we will discuss about the Intel EHCI specification [32]. While discussing we will focus on essential elements of EHCI description which are necessary for better understanding of host controller driver implementation. For detailed descriptions please refer to [32].

#### 5.1 Registers and Mackerel Interfacing

The EHCI controller has two different functional register sets. The first set called *capability registers* is responsible for laying out the capabilities of the host controller. The capability registers specify the limits, restrictions, and capabilities of the host controller implementation. These values are used as parameters to the host controller driver. It contains information such as such as number of ports, number of companion controllers (CC), routing logic, HC supports 32 or 64 bit etc. It also contains the starting address of memory region for the second set of registers called *operational registers*. The operational registers are used by system software to control and monitor the operational state of the host controller.

Mackerel [28] is device interfacing language. Mackerel compiler upon giving device interface related specifications generates C code to safely manipulate device state by reading or writing registers. Mackerel generated code is used for interacting with the HC registers. The capability register set is a variable length memory region and operational register set starts after it. Hence it is required to break single EHCI device into two separate devices: EHCI capability device and EHCI operational device. The Mackerel dev files ehci\_cap.dev and ehci\_op.dev contain registers specification for above mentioned two devices respectively. Upon initialization first EHCI capability device is initialized and operation register offset is read from it to initialize the EHCI operational device.

| Offset | Size | Mnemonic       | Description                                 |  |  |  |  |  |

|--------|------|----------------|---------------------------------------------|--|--|--|--|--|

| 00h    | 1    | CAPLENGTH      | Capability length register contains the be- |  |  |  |  |  |

|        |      |                | ginning of the operation register space.    |  |  |  |  |  |

| 02h    | 2    | HCIVERSION     | This register contains a BCD encoding of    |  |  |  |  |  |

|        |      |                | the EHCI revision number supported by       |  |  |  |  |  |

|        |      |                | the host.                                   |  |  |  |  |  |

| 04h    | 4    | HCSPARAMS      | This register contains set of fields that   |  |  |  |  |  |

|        |      |                | are structural parameters, like number of   |  |  |  |  |  |

|        |      |                | ports etc.                                  |  |  |  |  |  |

| 08h    | 4    | HCCPARAMS      | This register contains multiple mode con-   |  |  |  |  |  |

|        |      |                | trol control and addressing capability etc. |  |  |  |  |  |

| 0Ch    | 8    | HCSP-PORTROUTE | This is an optional register. If imple-     |  |  |  |  |  |

|        |      |                | mented then contains route mappings for     |  |  |  |  |  |

|        |      |                | companion controllers.                      |  |  |  |  |  |

Table 5.1: EHCI capability registers

Table 5.2: EHCI operational registers

| Offset | Size | Mnemonic         | Description                                 |  |  |  |  |

|--------|------|------------------|---------------------------------------------|--|--|--|--|

| 00h    | 4    | USBCMD           | Contains commands to be execute by the      |  |  |  |  |

|        |      |                  | controller.                                 |  |  |  |  |

| 04h    | 4    | USBSTS           | Reflects the pending interrupts and vari-   |  |  |  |  |

|        |      |                  | ous states of the controller.               |  |  |  |  |

| 08h    | 4    | USBINTR          | Enables or disables reporting of the corre- |  |  |  |  |

|        |      |                  | sponding interrupt to the software.         |  |  |  |  |

| 0Ch    | 4    | FRINDEX          | Contains the index into the periodic frame  |  |  |  |  |

|        |      |                  | list.                                       |  |  |  |  |

| 10h    | 4    | CTRLDSEGMENT     | Contains the higher [32-63] bits of EHCI    |  |  |  |  |

|        |      |                  | data structures.                            |  |  |  |  |

| 14h    | 4    | PERIODICLISTBASE | Contains the base address of periodic       |  |  |  |  |

|        |      |                  | frame list.                                 |  |  |  |  |

| 18h    | 4    | ASYNCLISTADDR    | Contains the address of next asynchronous   |  |  |  |  |

|        |      |                  | queue head to be executed.                  |  |  |  |  |

| 40h    | 4    | CONFIGFLAG       | Contains flags for port routing logic.      |  |  |  |  |

| 44h    | 4    | PORTSC           | Contains status of each USB port.           |  |  |  |  |

Table 5.1 and 5.2 gives and overview of the registers and their associated functions. Chapter 2 in EHCI documentation discuss in detail about these registers.

#### 5.2 Associated Data Structures

In this section we will discuss EHCI data structures used to communicate with control, status and data between controller driver (software) and controller hardware. We will focus on how asynchronous queue management is done in EHCI. All interrupt, control and bulk data streams are managed via queue heads (QHs) and queue element transfer descriptor (qTDs). These are queued in asynchronous queue for execution.

#### 5.2.1 Queue Element Transfer Descriptor (qTDs)

The qTDs are only used with the queue heads. These are used for one or more USB transactions. The structure block contains two link pointers for queue advancements and five data element array for buffer pointers. This structure must be physically contiguous and 32 bytes aligned. The table 5.1 shows the block diagram for the queue element layout. Please refer to the section 3.5 in EHCI documentation for detailed description.

| 31 30 29 28 27 26 25 24      | Novet of D point or      | 11 10 9 8 | 7 6 5 4 3 2 1 0 |  |  |  |  |

|------------------------------|--------------------------|-----------|-----------------|--|--|--|--|

| Next qTD pointer             |                          |           |                 |  |  |  |  |

| Alternate next qTD pointer 0 |                          |           |                 |  |  |  |  |

| at Total bytes               | s to transfer icc C_page | Cerr PID  | Status          |  |  |  |  |

| Buffer                       | pointer (page 0)         | Curre     | ent Offset      |  |  |  |  |

| Buffer                       | pointer (page 1)         | Reserved  |                 |  |  |  |  |

| Buffer                       | pointer (page 2)         | Re        | eserved         |  |  |  |  |

| Buffer                       | pointer (page 3)         | Re        | eserved         |  |  |  |  |

| Buffer                       | pointer (page 4)         | R         | eserved         |  |  |  |  |

| Host controller read/write   |                          |           |                 |  |  |  |  |

Host controller read only

Figure 5.1: qTD data block layout

The status field reflects the current status of the queue elements. Host controller writes back the qTDs only after the transfer retirement.

#### 5.2.2 Queue Heads (QHs)

A queue head is used to perform transfer on a particular endpoint on the USB device. A data transfer request is made to an endpoint by using a queue head and associated queue elements. A queue head can only have data transfer in one direction except on default endpoint which is bi-directional. The queue heads are linked to each other via physical address pointers to make a circular link list. This list is called asynchronous link list and controller hardware execute it in a strict round robin manner.

| 31 30 29 28 27 2                           |                                                         |                   |          |                            |       |        | 8            | 765      |          |

|--------------------------------------------|---------------------------------------------------------|-------------------|----------|----------------------------|-------|--------|--------------|----------|----------|

| Queue head horizontal link pointer 0 Typ T |                                                         |                   |          |                            |       |        |              |          |          |

| RL C                                       | Maxin                                                   | mum packet length |          | H dtc EPS EndPt            |       |        | I Device add |          |          |

| Mult Port Number Hub address               |                                                         |                   |          | uFrame C-mask uFrame S-mas |       |        |              | e S-mask |          |

|                                            |                                                         | Curren            | t qTD po | int                        | er    |        |              |          | 0        |

|                                            |                                                         | Next              | qTD poi  | nte                        | r     |        |              |          | 0 т      |

|                                            |                                                         | Alter             | nate nez | <mark>ct c</mark>          | ITD P | ointe  | er           |          | NakCnt T |

| dt Total                                   | bytes                                                   | to tran           | sfer     | ioc C_                     | page  | Cerr F | DI           | S        | tatus    |

| В                                          | uffer                                                   | pointer           | (page 0  | )                          |       | Cu     | rre          | ent (    | Offset   |

| B                                          | uffer                                                   | pointer           | (page 1  | )                          |       | Rsvo   | d            | C-pro    | og-mask  |

| Bı                                         | Buffer pointer (page 2) S-bytes FrameT                  |                   |          |                            |       |        |              | FrameTag |          |

| Buffer pointer (page 3) Reserved           |                                                         |                   |          |                            |       |        |              | ved      |          |

| Buffer pointer (page 4) Reserved           |                                                         |                   |          |                            |       |        | ved          |          |          |

|                                            | Host controller read/write<br>Host controller read only |                   |          |                            |       |        |              |          |          |

Figure 5.2: Queue head data block layout

The dword 1 in queue head contains endpoint characteristics including its address, maximum packet size and endpoint speed etc. The dword 2 contains endpoint capabilities but is mostly used in split transaction for low and full speed devices. The multiplier is used for high speed isochronous endpoints.

The host controller writable area as shown in figure 5.2 is called *transfer* overlay. Controller driver is only required to initialize the controller's readable area, except when driver is maintaining data toggle bit<sup>1</sup> in queue head which requires setting up 1 bit in the overlay. The overlay is automatically initialized by the queue element which hardware is executing currently. The current queue element pointer contains the address of that queue element. When the execution of queue element is finished the updated status if written back to the queue element to reflect the changes.

$<sup>^1\</sup>mathrm{Explained}$  in 5.3.5

The meaning and semantics associated with every field are explained in great detail in section 3.5 and 3.6 of EHCI documentation.

#### 5.3 Operational Model

In the previous section we explained about the data structures used to interact with EHCI hardware. In this section we will discuss how this interaction is done and how EHCI handles various responsibilities.

#### 5.3.1 Port Routing and Control

A EHCI controller can consists of one EHCI programming interface and 0 to N USB 1.1 companion host controllers. These are required to handle low and full speed devices. When such devices are detected the responsibility of handling them is delegated to one of the companion controller. The EHCI has port and status register for every port but companion controller has only the port control and status registers which it is required to operate. The port activity notification is first sent to the companion controller, if it exists.

The routing logic can be defined in two ways: a global policy or per port manner. The global policy is set by setting *configured flag* (CF) bit in CONFIGELAG register. Upon setting it, all port related activity notifications are sent to EHCI. On the other hand the port also can be delegated to companion controller by setting *port owner* bit in port status register. For current implementation the controller driver sets CF bit to 1 so that all notifications on port activity are routed to EHCI. Section 4.2 in EHCI documentation talks in detail how delegation and routing is done.

#### 5.3.2 Periodic Queue

The periodic queue contains elements from isochronous and interrupt transfers. It is scheduled in every micro-frame. Hence periodic schedule provides bandwidth and latency guarantees to the application. When a new micro-frame is started controller hardware always start execution by checking periodic frame list. If there are any more pending execution then they are executed first before moving on to the asynchronous schedule. A new request is only accepted when it is feasible to schedule it in periodic list with the current workload.

The current implementation does not support this. The section 5.6 in USB 2.0 documentation and section 4.6 and 4.7 in EHCI documentation discuss it in detail.

#### 5.3.3 Asynchronous Queue Management

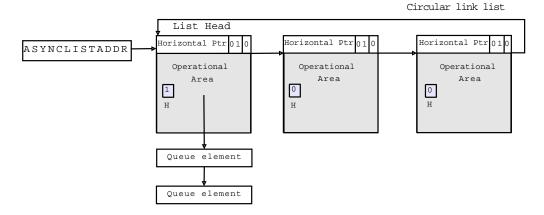

Asynchronous queue is where all the bulk and control transfer is managed. The host controller executes this list only when it reaches the end of the periodic schedule. The asynchronous list is a simple circular list of queue heads. The register AYNCLISTADDR register contains the pointer to the next queue head. Hence all en-queued queue heads are executed in a strict round robin manner.

Figure 5.3: Asynchronous queue in host controller

Figure 5.3 gives an overview how asynchronous list looks like. As shown in the figure the list always contains one queue head element which has H bit marked as 1. While traversing the list when controller hardware sees this bit set again, it knows that it has completed one iteration over the list. The host controller completes the processing of the list if one of the following events occur:

- End of the microframe occurs.

- Controller detects an empty list condition.

- The asynchronous schedule is disabled.

#### Node insertion

When inserting a new queue head into a activated asynchronous list software must ensure that schedule is always coherent from host controller's point of view. There should not be any invalid pointers in queue head as well as in linked queue elements. If queue head is the only element in the list then it should have head bit set. Actual logic for node insertion in the list is pretty much like insertion in a circular link list. See section 4.8.1 in EHCI documentation for details.

#### Node removal

Node removal from the list is more complex than insertion. The problem of node removal become complicated because of cached references to the removed node in the host controller hardware. Software must not remove any active nodes from the list. It should first mark them inactive and wait for hardware to reflect changes. Only then it should proceed to remove the inactive node.

A simple method is to disable the whole list and safely remove the marked node from the list. But this method has high overhead as for every removal driver has to disable whole active list.

A more elegant method called *handshake mechanism* ensures that controller hardware does not have any cached references to the removed node. This is a two step process. In the first step, the node to be removed is unlinked from the schedule by updating the linkage pointer but is not removed from the schedule. After unlinking from the schedule the driver sets *async advance doorbell* on host controller register. In step two, the driver will receive a notification (in form of an interrupt) that indicates that controller has traversed the whole list and now it does not have any cached pointers for nodes. At this point driver can remove the unlinked node from the schedule. Section 4.8.2 in EHCI documentation gives details about the node removal from the list.

#### 5.3.4 PING Protocol Maintenance

USB 2.0 uses PING protocol on bulk OUT endpoints on high speed devices. The purpose of the protocol is to avoid unnecessary bandwidth usage. USB devices are slower than host controller hardware. While doing a transaction on an OUT bulk endpoint, device needs some time to stabilize and absorb the incoming data by writing it to persistent storage. It is possible that data has been transferred to device but controller did not receive any valid response from the device. This inefficient mechanism leads to bandwidth wastage. To overcome such scenarios USB 2.0 employs the PING protocol.

For every bulk out transaction the controller hardware first sends a PING protocol packet to the device. If a device is ready to accept more data it sends acknowledgment otherwise negative acknowledgment (NACK) back to the controller for the PING packet. If device sends a NACK for PING the host controller remains in PING state and postpones sending data to the next attempt. All bulk OUT data transactions end in PING state unlike IN transactions which end in complete state. For more details of states and PING protocol please refer to section 3.5 and 4.11 in EHCI and section 8.5.1

in USB 2.0 documents.

#### 5.3.5 Data Toggle Synchronization

USB 2.0 uses data toggle protocol to ensure correct and orderly delivery of the data packets. The synchronization is achieved by using DATA0 and DATA1 type of data packets for delivery. The data toggle protocol works like stop-and-wait protocol with a window size of 1. After a successful reception of a data packet receiver toggles the packet bit. Similarly on the sender side when sender receives an acknowledgment for previously transmitted packet, it toggles its bit sequence. It is responsibility of the host controller driver to properly maintain these bits. The *data toggle* fields in queue elements and queue head will govern how these bit are manipulated. For bit field set to 1, DATA1 type packet will be used other wise DATA0.

The control transaction has specific requirements that command should always be DATA0 and status should be DATA1. The optional data stage is started with DATA1 and toggles with the number of packets. Similarly for bulk transactions after configuration and interface assignment the data toggle bits are set to zero. For every successful transaction the corresponding bit is toggled. Any mistake in data toggle maintenance can lead to obscure debugging situations which are hard to debug. If wrong data toggle bit is set into the transaction then host controller will not execute them and the system appears to be stopped, hence no other debugging techniques could help. Hence utmost care should be used when manipulating them.

Section 8.6 in USB 2.0 documentation gives details of the protocol and how synchronization is achieved over it.

### Chapter 6

# Distributed USB Infrastructure

#### 6.1 Overview

In this chapter we will describe in detail about our implementation of distributed USB infrastructure for Barrelfish. There are four basic blocks in the implementation:

- 1. USB Memory Manager: This module is primarily responsible for memory maintenance. The explicit memory management is required to meet the complex memory requirements of USB protocol. It is responsible for allocating memory for control data, requests and I/O buffers.

- 2. EHCI Host Controller Driver: The EHCI host controller driver (HCD) is responsible for interaction with the host controller hardware. It abstracts and shields all complexities of managing EHCI hardware and provides a clean interface for communication with it.

- 3. USB Manager: USB manager is responsible for all management related activities for USB such as pipe allocation, keeping track of USB topology, performing device enumeration, locating device drivers for new device etc.

- 4. **USB Client Driver:** After device enumeration the responsibility of device is handed over to the USB device driver also called USB client driver. The driver knows how to operate and what services are available on the device.

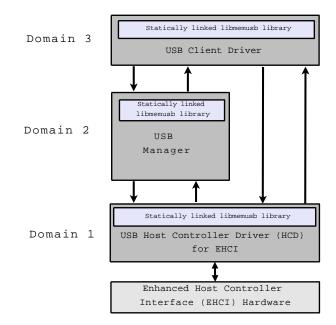

The figure 6.1 shows the overall architecture of the implemented USB system. All modules, except USB memory manager, run in separate domains. The USB memory manager is compiled as a statically linked library

Figure 6.1: Distributed USB infrastructure

to all three domains. The USB memory manager *can be implemented* as a separate domain but since all these module use it intensively for memory allocation it was decided to implemented it as a library. This design choice is good because every domain is responsible for managing its own memory usage. A notorious domain can crash USB memory manager by requesting a large chunk of memory which is first allocated on behalf of the memory manager. Crashing a single running instance of USB memory manager will effectively cease the execution of other domains also. Apart from unnecessary complexity of unmapping and mapping of capabilities across domains, USB memory manager, if implemented as separate domain, could also be a point of contention which is not desired from scalability perspective.

#### 6.2 Communication Between the Domains

All main three modules run a server instance, to export services provided by them. The communication is done as in a client-server architecture by message passing. Messages are passed using inter-domain communication primitives provided by Barrelfish namely IDC and URPC. Each server instance first registers its services to system wide service registry server called *Chips*. All clients of a particular server manage to find it by requesting service name to Chips. These internal details of server client communication mechanism are hidden by Flounder, a domain specific language (DSL). Flounder automatically generated the necessary back-end required to communicate with Chips and between a server and its clients.

#### Header File Services h func1(...) funcn(...) Client Side Server Side Implementatio Implementation funcl(...) func1(... Proxv for {... fun1 IPC(...); Inter Domain Communication via Message Proxy funcn(... Passing for funcn(... fun2 IPC( Server Domain Client Domain

#### 6.3 Proxy Function Implementations

Figure 6.2: Proxy interfacing on client side

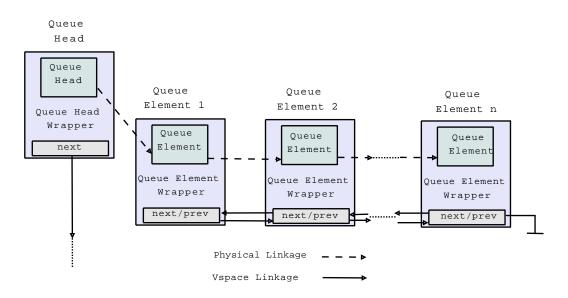

To shared relevant data structures and service functions, these pieces (prototypes) are moved to the header files. The definition of a particular service function depends on the domain. On server side a function is implemented in a normal manner. On the client side it is implemented as a proxy function. These proxy functions hide the internal server client communication mechanism from the top level logic. In every domain there are two layers of logic. The core logic is called *high level logic* which is the actual functionality implemented. The other, lower level logic, is responsible for taking care of communication and hiding other details. The figure 6.2 gives an overview of the implementation. The advantage of such design is that it completely decouples the communication logic from core logic of the implementation. It also improves readability because function names are same across the domains and new user can implicitly assume that control flow will *somehow* reach at the corresponding function in other domain. The inter domain communication is managed by the Flounder generated server client stubs.

#### 6.4 Synchronization

There is no need for explicit synchronization on the server for multiple clients. For server client model implemented in Barrelfish every message is delivered one by one in a message handler loop. Next message is fetched only after processing for the current message is completed. This basic design choices make sure that there are no need for explicit locks in case of multiple clients sending requests concurrently to the server.

#### 6.5 Hot-plugging

The implemented system is completely event driven. All participating modules wait for some activity or requests from higher layers. These modules just start as service servers. USB delivers activities from hardware as interrupts to the host controller driver. These interrupts drive further execution logic in the controller driver. Similarly other modules can be activated only upon demand. Upon no activity, these modules *can* be shutdown and unloaded (except for HC driver, which has interrupt handler required to get notifications on new activities) from the operating system. For example in current system implementation device driver starts as a server and waits for the *device found* notification. It could also be started only after when device is detected given that every executable contains same server name as its name.

## Chapter 7

## **USB** Memory Management

Barrelfish does not provide complex memory management operations to the user space applications. Each application is responsible for implementing such desired operations on a given basic set of capabilities by Barrelfish. These capabilities include, but not limited to:

- 1. Frame capability allocation. (assignments)

- 2. Mapping allocated frames to the virtual memory of applications. (map)

- 3. Revoking the capability containing frames. (delete)

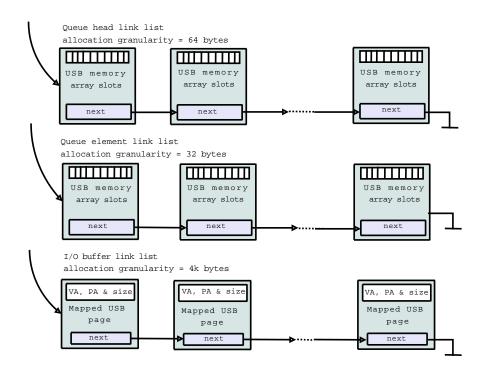

The USB system implementation has complex memory management requirements. It allocates chunks of memory on the demand, pretty much like the malloc system in GNU Linux. Though USB specification does not put this as a requirement but in implemented system I/O buffers have to be page aligned. For all allocated queue heads and queue elements linkage is done in virtual space as well as physical space. The virtual space linkage is required to keep track of memory usage. Linkage at physical level facilitates host controller hardware to traverse and execute queue elements one after another. All relevant data structures have to be contiguous and 32 bytes aligned in physical space (pspace). Also USB memory manager has to ensure that no EHCI controller data structure crosses 4kB frame boundary.

The implemented system does not have to be as comprehensive as malloc utility. It already knows that all allocation requests are for either queue heads (48 bytes) or queue elements (32 bytes). Fortunately, all other potential request segments (specifically in device enumeration) such as device descriptors and command sequences also fit in less than that. For example USB device descriptor is 18 bytes long, which can easily fit in one 32 bytes chunk. The EHCI data structures need queue heads and elements to be 32 bytes aligned. Thus in the implementation the queue head size is rounded from 48 bytes to 64 bytes. This rounding up generates internal fragmentation of 16 bytes per allocated queue head.