# Master's Thesis Nr. 4

Systems Group, Department of Computer Science, ETH Zurich

Support for heterogeneous cores for Barrelfish

by

Dominik Menzi

Supervised by

Adrian Schuepbach Andrew Baumann Timothy Roscoe

4. Oct 2010 - 3. Jul 2011

# Contents

| 1 | Intr | oduction                                        | 4      |

|---|------|-------------------------------------------------|--------|

|   | 1.1  | Motivation                                      | 4      |

| 2 | Bac  | 0                                               | 5      |

|   | 2.1  |                                                 | 5      |

|   |      | 2.1.1 IDC / Flounder $\ldots$                   | 5      |

|   | 2.2  | SCC                                             | 6      |

|   |      |                                                 | 6      |

|   |      | 2.2.2 Memory controller memory layout           | 8      |

|   |      |                                                 | 9      |

|   |      | 2.2.4 FPGA / System Interface                   | 1      |

|   |      | 2.2.4.1 Host-SCC messaging                      | 1      |

|   |      | 2.2.4.2 Benchmarks                              | 5      |

| 3 | Het  | erogeneous Support 1                            | 8      |

|   | 3.1  | •                                               | 8      |

|   |      | 3.1.1 Boot Process                              | 8      |

|   |      | 3.1.2 Communication                             | 9      |

|   |      |                                                 | 0      |

|   | 3.2  | Implementation                                  | 0      |

|   |      | 3.2.1 Cross-Architecture Boot                   | 0      |

|   |      | 3.2.2 Cross-Architecture Communication Protocol | 0      |

|   |      |                                                 | 1      |

|   | 3.3  |                                                 | 4      |

|   | 3.4  |                                                 | 6      |

|   |      |                                                 | 6      |

|   |      |                                                 | 6      |

| 4 | SIF  | MP - SIF message passing 2                      | 7      |

| - | 4.1  | - · ·                                           | 7      |

|   | 4.2  |                                                 | 7      |

|   | 1.2  | 1                                               | 8      |

|   |      |                                                 | 8      |

|   |      | J.                                              | 8      |

|   |      |                                                 | 9      |

|   |      |                                                 |        |

|   |      |                                                 | 9<br>9 |

|   |      | 4.2.2   | 4.2.1.5 Encapsulation |          |

|---|------|---------|-----------------------|----------|

|   |      | 4.2.3   | SIF                   |          |

|   |      |         | 4.2.3.1 Host Part     |          |

|   |      |         | 4.2.3.2 SCC Part      |          |

|   |      | 4.2.4   | Bootstrapping         |          |

|   |      |         | 4.2.4.1 SIF           |          |

|   |      |         | 4.2.4.2 Monitor       |          |

|   |      |         | 4.2.4.3 Inter-SIF     |          |

|   |      | 4.2.5   | RPC Clients           | <br>. 35 |

|   | 4.3  | Evalua  | ation                 |          |

|   |      | 4.3.1   | Benchmarks            | <br>. 36 |

|   | 4.4  | Future  | e Work                |          |

|   |      | 4.4.1   | Multicore SCC         |          |

|   |      | 4.4.2   | Data Prefetch         | <br>. 37 |

|   |      | 4.4.3   | SCC-Host messaging    | <br>. 37 |

|   |      | 4.4.4   | IPI                   | <br>. 40 |

|   |      | 4.4.5   | Routing               | <br>. 40 |

| 5 | Prot | ocol Se | election              | 41       |

| - | 5.1  |         | iew                   | <br>. 41 |

|   | 5.2  |         | mentation             |          |

|   | 5.3  | -       | ation                 |          |

|   | 5.4  | Future  | e Work                | <br>. 43 |

| 6 | Rela | ted Wo  | ork                   | 44       |

| 7 | Con  | clusion |                       | 49       |

| Α | sco  |         |                       | 50       |

| В | Ben  | chmark  | ۲S                    | 55       |

As computer hardware becomes more powerful and cheaper, hardware other than the CPU becomes suitable to run applications. This has been used to offload work to devices that are more suited for the workload, like highly parallelizable computing workloads that are offloaded to graphics cards.

Barrelfish is a "Multikernel", a new way of building operating systems that treats the inside of a machine as a distributed, networked system, and runs a different kernel, or "CPU driver", on every core.

This possibly makes Barrelfish highly suitable to run not only on a homogeneous set of CPUs and cores, but to include processors on peripheral devices, which may be of different architecture.

In this thesis I present two extensions to Barrelfish that allow it to be run on a heterogeneous set of CPU cores, either using x86\_64 and x86\_32 cores in one machine or using Intel's Single-Chip Cloud Computer to extend the set of cores available in a machine.

# **1** Introduction

# 1.1 Motivation

As computer hardware becomes more powerful and cheaper, hardware other than the CPU becomes suitable to run applications. This has been used to offload work to devices that are more suited for the workload, like highly parallelizable computing workloads that are offloaded to graphics cards.

Barrelfish is a "Multikernel" [BBD<sup>+</sup>09], a new way of building operating systems that treats the inside of a machine as a distributed, networked system, and runs a different kernel, or "CPU driver", on every core. Barrelfish also uses techniques like logic programming and constrained optimization to reason about hardware and devices [SSBR08].

This gives gives an approach to consider not only offloading applications and specific workloads to different devices, but possibly have the operating system span diverse hardware with different architectures, such as CPUs, GPUs, programmable NICs or other devices suitable for running an operating system.

In this thesis, I will demonstrate two versions of barrelfish that are able to run on heterogeneous systems. The first version, described in chapter 3, can run on x86\_64 and x86\_32 processors simultaneously. The second version, described in chapter 4, can run on a x86\_64 core on a host PC and on a x86\_32 core on a Intel Single-Chip Cloud Computer (SCC) simultaneously, connected by a Peripheral Component Interconnect Express (PCIe) bus.

# 2 Background

## 2.1 Barrelfish

Barrelfish is an operating system built in the Systems Group at ETH Zurich. It is built using a new architecture called "Multikernel" [BBD+09]. The kernel of the operating system is very similar to that of a microkernel in that it only provides the most basic functionality.

The multikernel differs from a microkernel based operating system in the way it works on multicore systems. Instead of having the kernel span all cores and protecting critical datastructures by locks from concurrent access, the multikernel runs a separate kernel on every core in the system.

In Barrelfish, these kernels do not communicate in any way with each other. On top of each kernel runs a service called "monitor", which creates connections to other monitors in the system and provides the basic functionality for applications to create connections to local and remote applications, drivers and other services.

### 2.1.1 IDC / Flounder

In Barrelfish, applications communicate over the inter-dispatcher communication (IDC) system. At its heart lies Flounder, an interface definition language. Flounder enables application writers to easily define interfaces to their services. A Flounder interface definition mainly consists of a number of definitions of messages.

From the interface definition, Flounder generates stub functions to call in an application and also implementations for each backend that was selected for a given application and architecture. At runtime, a connection is established using the appropriate backend implementation depending on the availability of hardware features such as shared memory, inter-processor interrupts and cache coherence.

After the binding process, the application can bind its own callbacks for receiving messages. When receiving a message, the callback is called with the arguments sent by the other side of the connection without the need of any conversion, extraction from or other manipulation of data structures. While a connection is initiated by a client, connecting to a server that exported the interface, the distinction between client and server disappears when the connection is established.

For Flounder, there exist a number of backend implementations that have different hardware requirements and purposes. For a list of the currently available backends, see table 2.1.

| Name    | Description                | Requirements for connection end- |

|---------|----------------------------|----------------------------------|

|         |                            | points                           |

| LMP     | Local Message Passing      | • Endpoints on the same core     |

| UMP     | User-level Message Passing | • Endpoints can share memory     |

|         |                            | • Cache coherence for shared     |

|         |                            | memory                           |

| UMP_IPI | User-level Message Passing | • Endpoints can share memory     |

|         | with inter-processor       | • IPIs between endpoints         |

|         | interrupts (IPIs)          |                                  |

| BMP     | Beehive Message Passing    | • Only available on the Beehive  |

|         |                            | processor                        |

| SIFMP   | SIF Message Passing        | • Protocol for communicating be- |

|         |                            | tween Intel Single-Chip Cloud    |

|         |                            | Computer (SCC) cores and con-    |

|         |                            | nected host processors           |

|         |                            | • see section $4$                |

Table 2.1: Flounder backends

# 2.2 SCC

## 2.2.1 Overview

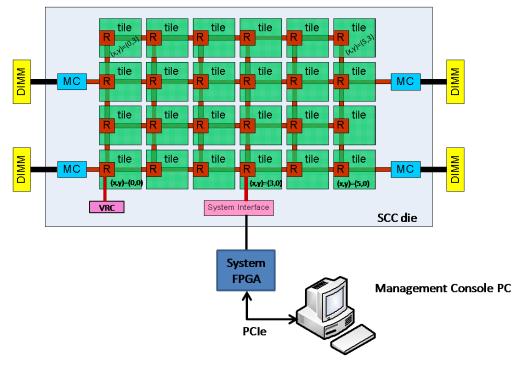

The Intel SCC, codename Rock Creek, is an experimental chip developed by Intel Labs <sup>1</sup>. Its name comes from the architecture of the SCC, which resembles that of a datacenter. The chip consists of 24 tiles, of which each contains two Intel P54C cores. The tiles are placed in a 6x4 mesh, connected by routers on each tile (see figure 2.1). The mesh is used for communication with other cores, connected hardware and for memory access. The SCC does not provide cache coherence.

The SCC has 4 DDR3 memory controllers, placed on the edges of the mesh, which control up to 16 GB of memory each, resulting in a maximum of 64 GB system memory. Additionally, there is message passing buffer (MPB) memory on each tile, giving each tile 16 kB of fast, local SRAM.

Each tile is connected to the mesh via a Mesh Interface Unit (MIU), that catches accesses to memory and translates *core addresses* to *system addresses*. It acts as a physical-to-physical memory mapping table and converts addresses using a lookup table (LUT). The LUTs are normally pre-configured by the host PC, but entries can also be changed at runtime by the operating system (OS). Entries in the LUT can point to memory regions in any of the 4 memory controllers, local and remote MPB memory, local and remote configuration registers and hardware interfaces.

<sup>&</sup>lt;sup>1</sup>http://techresearch.intel.com/ProjectDetails.aspx?Id=1

Figure 2.1: SCC Top-Level Architecture

The cores are numbered from 0-47, from bottom left to top right

From SCC External Architecture Specification, Revision 0.94

On memory access, the MIU forges a packet with the help of the LUTs and either sends it to a local destination (MPB, local configuration register) or forwards it to the routher on the tile, which forwards it to the appropriate destination. Destinations consist of the coordinates of a tile and a subdestination number (see table 2.2).

| Subdestination | Number | Comment                                    |

|----------------|--------|--------------------------------------------|

| Core 0         | 0x0    | Not a destination for memory R/W           |

| Core1          | 0x1    | Not a destination for memory $R/W$         |

| CRB            | 0x2    | Configuration Register                     |

| MPB            | 0x3    | Message Passing Buffer                     |

| East port      | 0x4    | @(5,0) and $@(5,2)$ is DDR3 MC             |

| South port     | 0x5    | @(3,0) is SIF, $@(0,0)$ is VRC             |

| West port      | 0x6    | @(0,0) and $@(0,2)$ is DDR3 MC             |

| North port     | 0x7    | Nothing is on this port of any edge router |

Table 2.2: SCC subdestination values

To facilitate the efficient use of MPB memory, Intel added an additional bit in the page tables (virtual-to-core-physical) which marks memory as message-passing buffer data. Memory which is marked as such will not be cached in the L2 cache and cached as write-back in the L1 cache. The SCC instruction set architecture (ISA) also contains a new instruction for use with this memory type. The instruction CL1INVMB invalidates all cache lines in the L1 cache that are marked as messagepassing buffer data. If the instruction is called before modifications to the L1 cache were written to memory, the data is lost.

The SCC is mounted on a field-programmable gate array (FPGA), which adds a management console reachable via telnet, controllers for solid state disks (SSDs), network access and a Peripheral Component Interconnect Express (PCIe) connection to a host PC. The host PC is used to initialize the hardware and to set up the OS to run on the SCC.

The documentation for the SCC is incomplete and only covers the high-level architecture of the chip. Most of the low-level details and functionality can only be reverse engineered from the source code of Intel's tools for the SCC  $^2$ . In the following sections, I will cover what I could figure out and what I used for the implementation of my driver.

### 2.2.2 Memory controller memory layout

Specified in the Intel SCC External Architecture Specification (EAS) are default memory mappings for setups with 16, 32 and 64 GB of system memory, which are used by the sccKit, the tools package provided by intel for use with the SCC. The

<sup>&</sup>lt;sup>2</sup>http://marcbug.scc-dc.com/svn/repository/trunk/

|   | Position | Port | Private Memory of Core # |

|---|----------|------|--------------------------|

| 0 | x=0, y=0 | West | 0-5, 12-17               |

| 1 | x=5, y=0 | East | 6-11, 18-23              |

| 2 | x=0, y=2 | West | 24-29, 36-41             |

current implementation of Barrelfish also assumes the default memory mapping for 16 GB of main memory (see table A.1).

Table 2.3: Locations of the four memory controllers

East

30-35, 42-47

The default memory mapping is used for every core and each core's private memory is mapped to a different system memory region and memory controller (see table A.2).

### 2.2.3 Write-combine buffer

3

x=5, y=2

To reduce write accesses to MPB memory, the SCC uses a write-combine buffer. As the functionality of this buffer is not covered by the Intel documents, it can lead to unexpected results.

To figure out the exact functionality of the write-combine buffer, I did a number of tests with the following setup:

The host PC booted an image of Barrelfish on the SCC and immediately started checking a predefined cacheline for changes by issuing non-cacheable read requests via the FPGA (see section 2.2.4). This way, the host PC was able to monitor the data in main memory without any intervening caches. As soon as it detected a change, it notified me of the changed data.

The image that was booted on the SCC was configured so that it would not use any memory mapped as MPB. The boot process was configured so that it mapped the frame with the predefined memory location and carried out the steps as in table 2.4. The numbers in the table indicate the order of the steps, while the letters denote branches that were carried out separately with a clean setup each.

#### Results

The results of these tests led to the conclusion that the write-combine buffer works on a complete cacheline as assumed and is activated if and only if the memory is mapped as MPB memory, independent of the actual memory hardware type. The write-combine buffer also acts as a cache for a single cacheline and is unaffected by the CL1INVMB instruction. The buffer is flushed when a write to a different cacheline mapped as MPB memory occurs or when each byte on the cacheline was written at least once.

| Step #         | Description                                              | Success? |

|----------------|----------------------------------------------------------|----------|

| 1              | write part of the cacheline                              |          |

| 2.a            | write the rest of that cacheline                         | yes      |

| 2.b            | write another cacheline on the same page                 | yes      |

| 2.c            | write to the stack                                       | no       |

| 2.d            | write to a global variable                               | no       |

| 2.e            | write to a second page mapped as MPB                     | yes      |

| 2.f            | do a CL1INVMB and write to a second page mapped as       | yes      |

|                | MPB                                                      |          |

| $2.\mathrm{g}$ | do a CL1INVMB and write to a second page not mapped      | no       |

|                | as MPB                                                   |          |

| $2.\mathrm{h}$ | do a CL1INVMB, write to a second page not mapped as      | yes      |

|                | MPB and write to a second cacheline on the first page    |          |

| 2.i            | write to a second page not mapped as MPB, that is on     | no       |

|                | a different memory controller                            |          |

| 2.j            | write to a second page mapped as MPB, that is on a       | yes      |

|                | different memory controller                              |          |

| 2.k            | read the whole cache line into a buffer, write the whole | yes      |

|                | cache line from the buffer                               |          |

| 2.1            | write part of the cacheline repeatedly                   | no       |

Table 2.4: Write-combine buffer functionality test steps

### 2.2.4 FPGA / System Interface

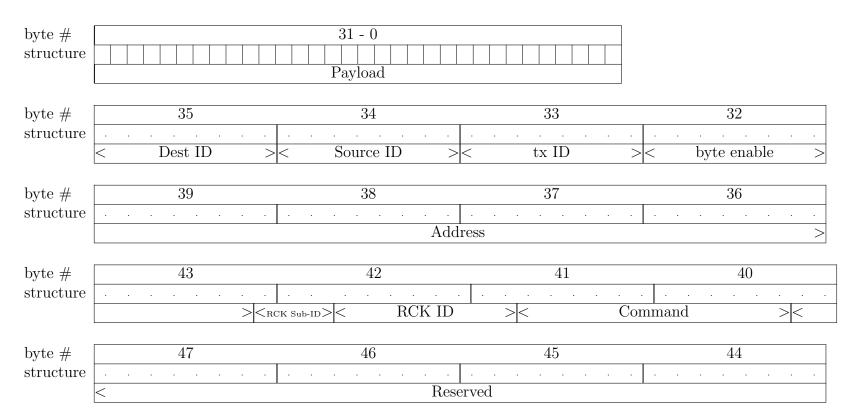

The Rocky Lake or Copperridge FPGA is connected to the host PC as a PCIe device and provides access to the SCC via the chip's System Interface (SIF). The host PC can send messages through the FPGA directly to routers in the mesh and thus to every memory location on the SCC. While the messages used in the mesh, called flits, are of variable length, the message sent to the SIF are 48 bytes long with a header length of 16 bytes, leaving 32 bytes for payload. They can be transmitted using programmed input/output (PIO) or the builtin direct memory access (DMA) engine.

#### 2.2.4.1 Host-SCC messaging

The FPGA has 2 FIFO queues for input and output. For these two queues, there is one 32-bit status register (trnct4), divided into input and output part. Both parts are 16 bits wide and consist of a 15-bit counter and an error bit. The counter indicates the number of 8-byte words in the queue. The maximum number of bytes in the queue can be read from a 32-bit read-only register.

To send a message, using either PIO or DMA, the input counter has to be checked first to ensure that the queue is not full. When the output counter has a value greater than zero, a message is pending and should be received by polling by the host PC.

SIF messages are sent to the appropriate destination by the FPGA using the mesh on the chip through the SIF after the messages have been converted to flits. Response flits are sent back to the SIF and converted by the FPGA to the 48-byte message format.

Most of the information in this chapter is extracted and reverse-engineered from the sources of Intel's sccKit, the set of tools provided by Intel for use with the SCC, since the host-SCC messaging is not documented in any way.

**Message format** The message format for all messages sent and received over the SIF is the same. All messages are 48 bytes long, with a payload size of 32 bytes and a header size of 16 bytes. Most messages don't use the full 32 bytes for payload.

All message types in use work with an address alignment of 8 bytes. Not aligned addresses in messages are truncated along the way and changed to the next lower 8-byte alignment border. The only exception from this is the WBI command, which uses a 32-byte address alignment.

Read operations (NCRD command) do not use the payload part of the message at all and their responses (DATACMP command) use only the first 8 bytes of payload and bytes 8-15 for some additional data from the same cacheline. This additional data, however, is not used by Intel's sccKit, thus can not be deemed safe to use.

Write operations (NCWR command) use only the first 8 bytes to transmit data. The NCWR command is the only operation in use that uses the *byteenable* header field to determine which bytes should be written. Write operations do not generate a response.

#### 2 Background

|                | Size     | Description                                                                                                                                 |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                | 32 bytes | Payload                                                                                                                                     |

| byteenable     | 8 bits   | For write operations, each bit can be set individually to indicate whether the byte should be written. A pattern of $0^*1+0^*$ is expected. |

| tx ID          | 8 bits   | unused                                                                                                                                      |

| source ID      | 8 bits   | The ID of the sender of the message. When<br>sending from the host PC, this is to be set to<br>0.                                           |

| destination ID | 8 bits   | The ID of the receiver of the message. When sending to the SCC, this is to be set to 1.                                                     |

| address        | 34 bits  | The address field has to contain the <i>system address</i> of the memory location to read or write.                                         |

| command        | 12  bits | See table 2.6.                                                                                                                              |

| rck ID         | 8 bits   | The rck ID is of the form (y:4 x:4), where (x, y) are the coordinates of the destination tile.                                              |

| rck sub-ID     | 3 bits   | The sub-ID denotes the destination port of the router (see table 2.2).                                                                      |

| reserved       | 5 bytes  |                                                                                                                                             |

Table 2.5: Host-SCC message format fields

For a schematic view of the message format, see table A.3

Cacheline write operations (WBI command) use the full 32 bytes payload to write a whole cacheline on the SCC.

For a description of all the header fields, see table 2.5.

For all message types and their description, see table 2.6.

**PIO** The FPGA provides an easy to use but slow method of transferring messages with PIO. For message input, the 32-bit registers *trnct2* and *trnct3* have to be written in turn, to effectively write 8-byte chunks of messages. Receiving messages is done in a similar way, by reading the registers *trnct0* and *trnct1* in turn.

PIO has no setup time, thus no overhead when a single message is transmitted, but it is not fast enough to transmit large amounts of data.

**DMA engine** The SCC board has a built-in Xilinx DMA engine that can be used to read and write messages on the FPGA.

A DMA transfer is initiated by first resetting the DMA engine, configuring it by writing configuration values to read or write configuration registers and starting it by writing the correct bits to the control register.

| Name       | Command $\#$ | Description                                   |

|------------|--------------|-----------------------------------------------|

| DATACMP    | 0x04f        | Response with data                            |

| NCDATACMP  | 0x04e        | SysIF specific: NCRD Response with data       |

| MEMCMP     | 0x049        | Only Ack no data                              |

| ABORT_MESH | 0x044        | Abort                                         |

| RDO        | 0x008        | Burst line fill (Read for ownership)          |

| WCWR       | 0x122        | Memory write $(1,2,4 8 \text{ bytes})$        |

| WBI        | 0x02C        | Cacheline write / Write back invalidate       |

| NCRD       | 0x007        | Non-cacheable read $(1,2,4,8 \text{ bytes})$  |

| NCWR       | 0x022        | Non-cacheable write $(1,2,4,8 \text{ bytes})$ |

| NCIORD     | 0x006        | I/O Read (sent by SCC cores)                  |

| NCIOWR     | 0x023        | I/O Write (sent by SCC cores)                 |

Table 2.6: Host-SCC message format fields

Whether the transfer is completed can be checked in the control register, or by waiting for an interrupt from the PCIe device. In the current implementation of the *sif* driver (see section 4.2.3), the completion of the DMA transfer is checked with the control register, doing a busy waiting until the transfer is finished. The driver does not use interrupts at the moment, because the interrupts do not arrive reliably (see paragraph DMA Interrupts).

For a complete set of steps for a DMA transfer, see tables 2.7, 2.8.

The information about the DMA engine was extracted from Intel's sccKit and from Xilinx XAPP1052 Bus Master DMA Performance Demonstration Reference Design for the Xilinx Endpoint PCI Express Solutions, which seems to discuss the DMA engine used on the SCC FPGA or a device that is very similar.

**DMA Interrupts** The Xilinx DMA engine on the Rocky Lake board can be configured to send an interrupt when a DMA transfer is finished. Intel's sccKit tools use it in a very simple way to avoid busy waiting for the end of the transfer:

Before the DMA transfer is started, a variable is set to *false* and when the PCIe device is initialized, an interrupt handler is registered that sets the variable to *true*. After the initiation of the transfer, a loop is entered that is exited as soon as the value in the variable is *true*.

I implemented the same pattern for the *sif* driver, but apparently some part in the system could not keep up with the number of interrupts and only the first interrupt was received by the driver. However, seemingly random added instructions to make the driver slower, like printf or loops, could resolve the issue.

A small test showed that the kernel did get all the interrupts and attempted to send them to the driver: Instead of waiting for the value of the variable to become *true*, I modified the driver to do busy waiting on the control register until the transfer was complete and not attempt to handle any interrupts. With this modification,

| Step | Operation                 | Register Operation | Value       |

|------|---------------------------|--------------------|-------------|

| 1    | Assert initiator reset    | Write DCR1         | 0x00000001  |

| 2    | De-assert initiator reset | Write DCR1         | 0x000000000 |

| 3    | Write hardware memory ad- | Write RDMATLPA     | address     |

|      | dress                     |                    |             |

| 4    | Write TLP size            | Write RDMATLPS     | TLP size    |

| 5    | Write TLP count           | Write RDMATLPC     | TLP count   |

| 6    | Write DMA start           | Write DCR2         | 0x00000001  |

| 7    | Wait for interrupt (Check | (Read DCR2)        | 0x00000100  |

|      | for completion bit)       | ```                |             |

Table 2.7: DMA transfer read steps

| Step | Operation                 | Register Operation | Value       |

|------|---------------------------|--------------------|-------------|

| 1    | Assert initiator reset    | Write DCR1         | 0x00000001  |

| 2    | De-assert initiator reset | Write DCR1         | 0x000000000 |

| 3    | Write hardware memory ad- | Write WDMATLPA     | address     |

|      | dress                     |                    |             |

| 4    | Write TLP size            | Write WDMATLPS     | TLP size    |

| 5    | Write TLP count           | Write WDMATLPC     | TLP count   |

| 6    | Write DMA start           | Write DCR2         | 0x00010000  |

| 7    | Wait for interrupt (Check | (Read DCR2)        | 0x01000000  |

|      | for completion bit)       |                    |             |

Table 2.8: DMA transfer write steps  $% \left( {{{\rm{Table}}} \right)$

the driver did receive all the interrupts, but after all the DMA transfers had been completed.

As I could not get it to run without adding extra instructions in the DMA code, I changed the driver to use busy waiting on the control register by default, but it can be configured to use interrupts instead.

#### 2.2.4.2 Benchmarks

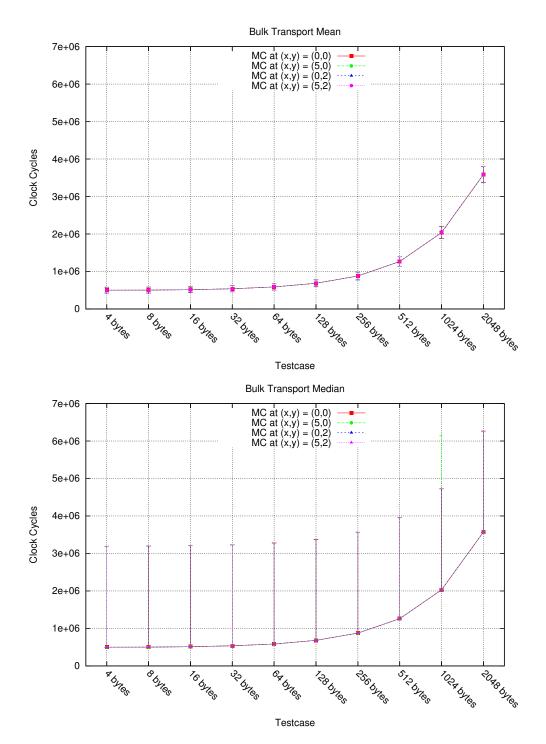

I did some benchmarks on the SCC to test the speed of the PCIe connection to SCC memory. I tested the time needed to read chunks of memory from SCC memory from all memory controllers to see how transmission times increase with bigger chunk sizes and to see if there are any differences between the connections to the memory controllers. I also tested the time needed to read from MPB memory of different cores to see if there are any differences between memory close to the SIF and memory far away from the SIF.

All the benchmarks were done using DMA, PIO was not used.

**Memory Controllers** The benchmark of the memory controllers consisted of bulk read procedures of 4, 8, 16, ... 1024, 2048 bytes. Each test was completed with a 99.9% confidence interval for the mean of less than  $\pm 1\%$ .

From the benchmarks I can conclude that the read operations over the PCIe bus have a part that requires a constant amount of time and a part that is linear to the size of the chunk read. From the data I can see that the constant part of the transmission times takes about 50000 host clock cycles. For small chunk sizes (< 64 bytes) the constant part of the transmission time dominates the overall transmission time and transmission times do not vary much (see figure 2.2).

From the benchmarks I can also conclude that reading from different memory controllers does not change the time needed to read data.

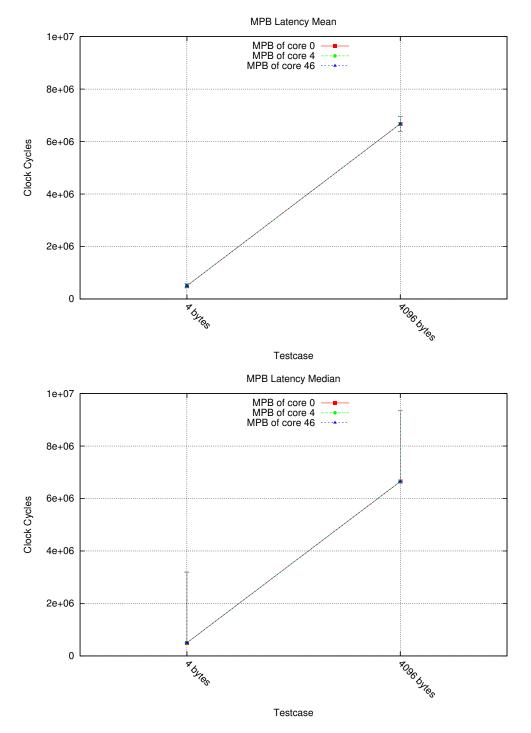

**MPB memory** The benchmark of the MPB memory consists of read operations of 4 and 4096 bytes from MPB memory of the cores 0, 4 and 46. All tests were completed with a 99.9% confidence interval for the mean of less than  $\pm 1\%$ .

Core 0 is the core that is booted first by default. Core 4 is the core that is closest to the SIF and core 46 is one of the cores that is the furthest from the SIF.

The benchmarks show that the time for reading from MPB memory on different cores does not differ or the difference is too small to be of any significance (see figure 2.3).

Figure 2.2: SCC main memory bulk transport read times

Figure 2.3: SCC MPB memory read times

# **3 Heterogeneous Support**

# 3.1 Overview

To create an OS that is able to span different architectures, a few things are required:

- The OS must be able to start cores of different architecture.

- There must be a communication protocol that is independent of architecture or performs the required conversions.

- The system must be able to start applications on cores of different architecture.

## 3.1.1 Boot Process

In Barrelfish, the booting of all cores that should run a cpu driver happens during the boot process of the bootstrap core. Cores can at the moment not be added to the system at runtime and so the boot process is important in creating a heterogeneous system. For this reason, I will first describe the startup process of Barrelfish in a homogeneous system.

- 1. On core 0 the bootloader starts and loads all modules that are necessary for the system to start over the network into memory. After that, the bootloader starts the kernel with command line arguments that indicate to the kernel that it runs on the bootstrap core. Part of the command line arguments is the memory address of a data structure containing records of all modules that were loaded by the bootloader.

- 2. The kernel initializes the cpu and relocates itself to a different virtual memory region.

- 3. Following that, the kernel starts *init*. Init starts the *monitor* and *mem\_serv* and helps them connect to each other.

- 4. When the monitor on the bootstrap core starts, it first connects to mem\_serv and initializes its rpc service. It then spawns the nameservice, *chips*, followed by all the modules that have the "boot" command-line argument specified in the bootloader's config file.

- 5. One of the "boot"-modules is *spawnd*. Spawnd provides the service to start processes and is therefore essential for the system if programs should be spawned after the boot process is over. On the bootstrap core, spawnd also starts the boot process on other cores. For each core it decides to boot (specified either by command-line arguments or detected automatically), spawnd sends a boot request to its local monitor and waits until a spawnd process has started on the new core and registered itself with the nameservice.

- 6. When the bootstrap monitor receives a boot request, it copies the Executable and Linkable Format (ELF) file of the kernel to a free memory region and initializes the binary. It allocates a new frame for a UMP connection and passes its memory address to the new core as argument.

On the cores booted by spawnd the bootprocess is slightly different:

- 1. After the kernel is booted, it does not spawn init, but directly the monitor.

- 2. Before the monitor can provide its services, it needs a connection to the bootstrap monitor. It does that by creating a UMP connection with a frame whose address it was given as a command-line argument. The frame is also known to the bootstrap monitor, which creates the other endpoint of the UMP connection.

- 3. Once the connection is established, the monitor on the app core can continue its initialization by connecting to mem\_serv first.

- 4. To start its own local spawnd, the monitor requests the image of spawnd from the bootstrap monitor.

### 3.1.2 Communication

When a connection between two cores is made in Barrelfish, the Flounder backend used is UMP. Because connections spanning multiple cores do not have the possibility to pass message arguments in registers, UMP uses a shared frame to transmit the messages.

When a process sends a message over a UMP connection, the process calls the function for the specific message. This function copies the message arguments to a connection-specific struct and calls the marshalling function. The marshalling function writes message packages into a ringbuffer that is located in the shared frame. It takes each argument and writes it in an array of pointer-sized words or splits and combines arguments to make best use of the available space. This array fills the complete space available for payload in a message package. On the other side of the connection, the unmarshalling function takes these words and builds the message arguments out of them. Capabilities are handled separately. The reference to a capability is sent to the monitor so that the monitor can send the actual capability to the monitor of the target processor and the other endpoint can receive the reference to its local capability from the monitor.

### 3.1.3 Application Start

To start a new process, regardless of the target core, the starter process uses the *lib-barrelfish*. This library provides convenience functions to communicate with *spawnd*, the spawn daemon. By using these functions, the starter process connects to spawnd on the target core and sends a message to load and run a certain binary. Part of this command is the *env* array, which contains all the environment variables set in the starter process, like *PATH*. The PATH variable is also used by the library to search for the binary of the given name, so that it can send spawnd the path to it.

Spawnd then connects to *ramfs* to look for a binary that matches the given path, loads it using either a shared frame for bulk transport or Flounder messages, and runs the process on its core.

# 3.2 Implementation

### 3.2.1 Cross-Architecture Boot

In the architecture of Barrelfish, the points where the implementation depends on the architecture are few. They are mainly the locations where a binary is selected, transmitted or installed or the actual hardware is used and configured. This greatly helped in developing a version of Barrelfish that is able to span x86\_64 and x86\_32 cores.

To get a heterogeneous OS, I had to change the interface of the monitor, so that spawnd can not only select which cores to boot, but also tell the monitor of which architecture they are. Similarly, the monitor on the new core needs to be able to tell the bootstrap monitor which binary of spawnd it requires, which I could also accomplish with a change of the monitor's interface.

### 3.2.2 Cross-Architecture Communication Protocol

The marshalling process works very well if both endpoints are of the same architecture, but if they are different, this ceases working, because the words in the payload array might not have the same size due to size differences of pointers and thus the arguments may be grouped differently. Also, arguments may themselves be of different size, like Barrelfish's error values, which are pointer-sized.

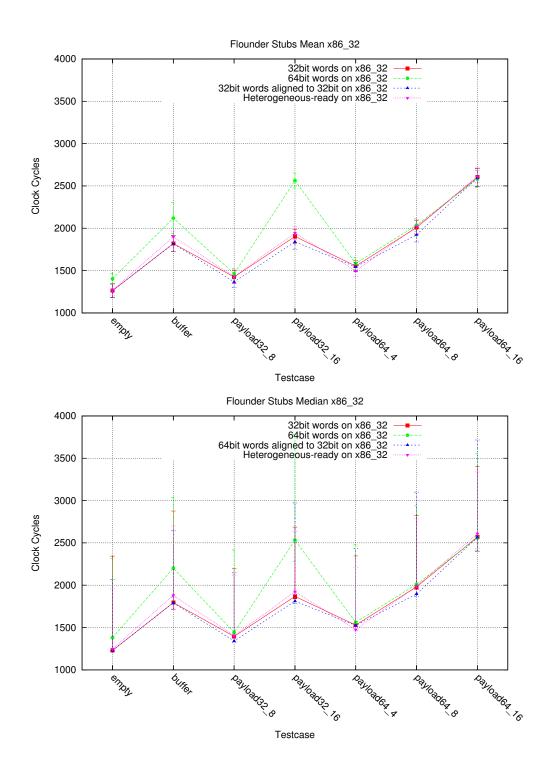

For this reason, I decided that when communicating between cores of different architecture, UMP should use the same word size for grouping message arguments and the message arguments should be converted to architecture-independent types. As I was working with x86\_32 and x86\_64, the obvious choices for payload array word sizes were 64 bit and 32 bit. I benchmarked versions of UMP with 32 bit word sizes and 64 bit word sizes and compared their speed to the original implementation. Additionally I created a version of UMP that splits, combines and groups words as if it would write 32 bit words, but combines them if necessary to write pointer-sized words, i.e. on x86\_64 it combines two 32 bit words and writes a 64 bit word to memory, because I wanted to be able to use the optimized 64 bit capabilities of the x86\_64 architecture.

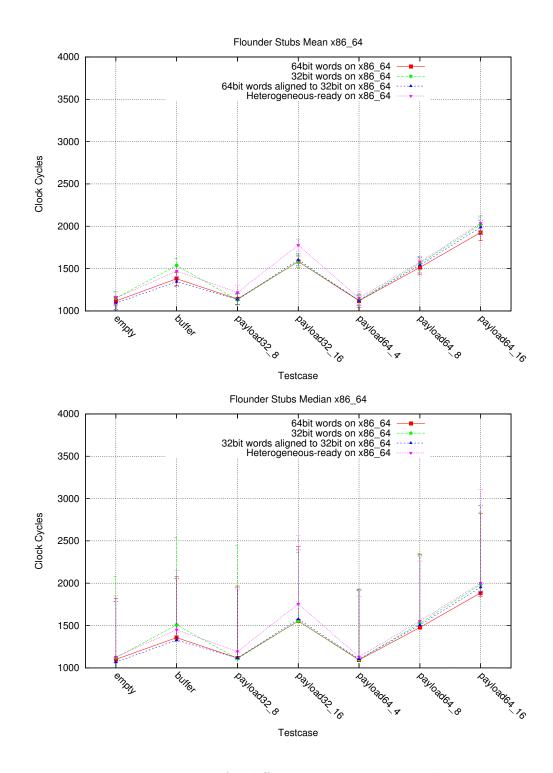

As can be seen in figures 3.1 and 3.2, the implementation that uses pointer-sized words to write the marshalled arguments into memory, but groups them as 32 bit words in any case, is the fastest and so chosen for my heterogeneous implementation.

The greatly increased transmission times of the 64 bit version on x86\_32 for the *payload32\_16* testcase, I can't explain. The message uses two message packages and should, extrapolated from the *payload32\_8* testcase, not be significantly slower than the original implementation.

Also, the increased transmission times of the 64 bit version on x86\_32 for the *empty* testcase is unexpected, because apart from the word sizes and the resulting change in the marshalling functions, nothing was changed and this testcase should not do any marshalling.

The increased transmission times of the 64 bit version on x86\_32 for the *buffer* testcase can be explained by the functioning of the buffer marshalling function. This function reads individual bytes from the buffer, ORs them together in a register and writes this word into the payload array. With the 32 bit sized registers available on x86\_32, these operations might take more time when a 64 bit word is manipulated. However, I did not test if this is the true source of the increased transmission time.

To be able to correctly transmit architecture-dependent types, every message argument is converted to its architecture- independent counterpart and saved in a struct that is very similar to the usual struct UMP uses for storing the message arguments, but stores architecture-independent types. The marshalling that is called is not the regular marshalling function, but one that is aware of the possibly different sizes of the new types and marshalls the message arguments accordingly. On the receiver side, I did the same, so a different unmarshalling function is used and the arguments are converted to the architecture-specific types before the registered callbacks are called.

### 3.2.3 Cross-Architecture Application Start

When a new process should be started on a core of different architecture, spawnd on the target core has to load the binary of the correct architecture. If the starter process calls the libbarrelfish, the library uses the PATH variable of the starter process to look for the binary. When the architecture of the source ant target cores is not the same, libbarrelfish looks in directories with binaries of the wrong architecture type. It may fina a binary with the correct name and instruct spawnd to run it. This of course fails and the starter process receives an error message.

Figure 3.1: Transmission times for different payload array word sizes on x86\_32

Figure 3.2: Transmission times for different payload array word sizes on x86\_64

A workaround for this is to supply libbarrelfish with the full path to the binary instead of only its name. This way, it ignores the PATH variable of the starter process and loads the correct binary.

This is only a temporary solution and if heterogeneous systems should become a normal part of Barrelfish, a more robust and flexible solution is needed.

A possible solution would be to add paths to the PATH variable that contain binaries for other architectures. The libbarrelfish would then be able to find a binary that matches the name as well as the architecture. The downside of this would be that the starter process needs to know the architecture of the target core and be able to search for the binary, but this may not be possible if the binaries are stored on a file system only accessible by the target core.

To avoid this problem, it may be possible to move the searching from the libbarrelfish to spawnd and let the target core decide whether a binary matches the core's architecture.

Another possibility would be to standardize binary paths. At the moment all binaries for a certain architecture are in the directory /<arch>/sbin/. A naming scheme that is more flexible could be created so that searching for a binary would become faster, because less directories have to be checked and less binaries have to be checked for matching architectures.

# 3.3 Evaluation

The heterogeneous implementation of UMP is slower than a pure UMP implementation, as can be seen in figures 3.1 and 3.2. This is expected, as the heterogeneous-ready implementation has an overhead with converting and correctly aligning message arguments to an architecture-independent format. The overhead in terms of transmission speed is about 1%-4% for messages transmitted between x86\_32 cores and about 5%- 12% for messages transmitted between x86\_64.

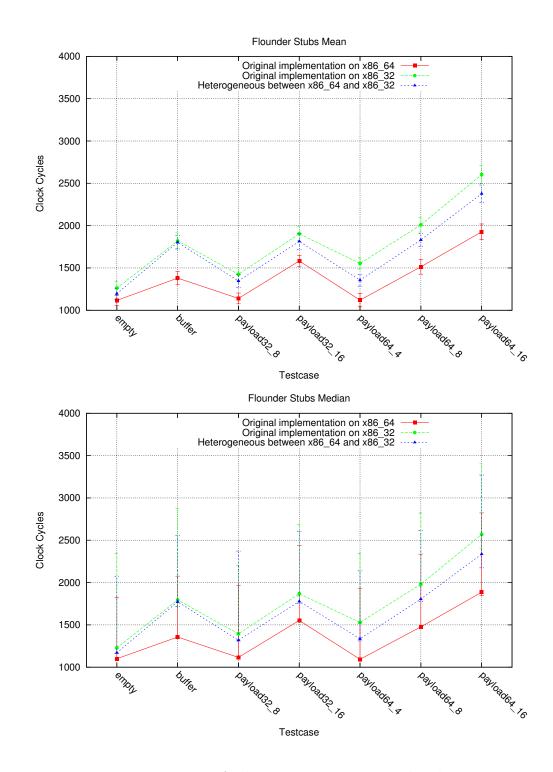

The transmission times of heterogeneous connections between x86\_64 and x86\_32 cores are higher than the times of homogeneous connections between two x86\_64 cores but lower than the times measured for homogeneous connections between two x86\_32 cores. It is expected that the heterogeneous connections are not as fast as connections between x86\_64 cores, as those connections do not perform conversion, but that is not the main contributor to the great difference between those two connections. As half of the work for the heterogeneous connection is done on the x86\_32 core, which does not have the same possibilities in terms of instructions and number of registers as the x86\_64 core and which therefore is slower, the heterogeneous connection speed is between the two homogeneous connection speeds (see figure 3.3).

The speed could probably still be increased slightly with an optimized marshalling process that writes a 64 bit chunk of a message argument as a 64 bit word directly instead of splitting it into two 32 bit words and combining them again for writing into the payload array.

Figure 3.3: Transmission times of a heterogeneous compared to homogeneous connections

# 3.4 Future Work

## 3.4.1 Endianness

The heterogeneous version of UMP is not completely ready for connections between different endiands yet. It is at the moment optimized and tested for little endian and may also need some adaptions for connections between big endian architectures only.

In any case, when a new architecture is to be supported by heterogeneous UMP, regardless of the architecture's endianness, new conversion functions have to be added so that variables on the new architecture can be converted to architecture-independent types.

# 3.4.2 Capabilities

Capabilities are at the moment not converted in any way when transmitted between cores of different architecture. The conversion of capabilities would have to be done in the monitor as that is the only place in the connection where the actual capability is available rather than a reference to it. Between x86\_64 and x86\_32, capabilities do not require any conversion, because the datastructures have the same types on both architectures and also have the same representation in memory. This is also the reason why I did not concentrate on that topic any further, but decided to begin working on a connection to the SCC.

However, even if capabilities can be transmitted without conversion, they are not necessarily valid on another core. Frame capabilities from a x86\_64 core for example are not valid on an x86\_32 core if the frame contains memory locations above 4GB. This would probably have to be resolved with the help of the *skb*.

# 4 SIFMP - SIF message passing

The Intel SCC is a research chip developed to give researchers the possibility to work with an architecture that might be the future of all processor chips. Specifically the unavailability of cache coherence and the non-shared memory impose restrictions on OSs and applications that run on this kind of processor. (See chapter 2.2 for more information on the SCC)

As Barrelfish already treats each core in a system as separate entities rather than a multi-threaded environment, Barrelfish should be perfectly suited to run on such a kind of chip. A version of Barrelfish that runs as one OS, spanning the whole chip already exists, so it seems natural to try and connect the SCC and the host PC to create an OS that spans both.

In this chapter I will describe the functioning of a communication protocol that enables processes to talk to each other even if they are on opposite sides of the PCIe bus that connects the SCC to the host PC.

# 4.1 Overview

For the communication protocol, there were a few requirements:

- 1. The SCC is attached to the host as a PCIe device, so it needs a device driver to access and configure it. The communication necessarily involves the driver.

- 2. The communication protocol should be integrated into the existing IDC framework, i.e. an extension to Flounder.

- 3. As the communication between the host and SCC cores is part of the boot process, a communication channel has to be opened without an external communication channel or manual configuration.

# 4.2 Implementation

The protocol used to connect processes on the host PC to processes on the SCC is called *SIFMP*, for *SIF message passing. sif* is the name of the driver for the SCC FPGA and stands for *System Interface*, the port on the SCC that connects it to peripheral devices.

### 4.2.1 Possible Communication Schemes

For communication protocol across a PCIe bus, a number of different approaches seemed possible, which I will describe in this section.

#### 4.2.1.1 Double Proxy

The *Double Proxy* version of SIFMP uses a driver on both sides of the PCIe bus.

Processes that want to create a connection to another process on the other side of the bus allocate a channel from the driver and register the connection to the driver as the notification channel.

Part of the allocated channel is a frame the allocating process gets from the driver, that is used as ringbuffer as with UMP. When the process sends a message, it writes the message in the ringbuffer and sends a notification to the driver, which copies the message to a similar frame on the other side of the PCIe bus and forwards the notification to the receiver of the message.

The process allocating a channel receives a channel identification number, which is sent to the other endpoint of the SIFMP connection so the other process can request its local frame for the ringbuffer and register a connection to the driver as notification channel.

This version is very symmetric from the processes' point of view, but uses two frames and two non-SIFMP connections for every SIFMP connection.

#### 4.2.1.2 Double Proxy, Notificationless

This version of a communication scheme is very similar to the *Double Proxy* version, but does not use notifications.

When a new SIFMP channel is created, it is normally registered on the default waitset. A channel registered on a waitset can either be idle, polled or pending.

If a channel is in idle state, there are no pending messages on that channel and the channel will not be checked when a message handler loop for that waitset is entered.

In pending state, a channel does have pending messages, which will be delivered as soon as the waitset is processed.

Channels marked as polled may have channels pending, but they are not marked as pending, because the channel state is not updated when a message arrives. When checking the waitset for pending messages, each channel marked as polled has to be checked individually.

In the *Double Proxy* version, SIFMP channels are registered on a waitset as idle, because they are triggered by notifications sent by the *sif* driver. A version without the notifications needs to register the channels as polled. On the host PC this simply results in a protocol that is more similar to UMP than to UMP\_IPI. On the SCC however, UMP does not work, because there is no cache coherence for shared memory, so the ringbuffer frames either have to be mapped as uncached or a method to cause a cache flush has to be added, which is very similar to a notification system. Also, there is an additional overhead for at least the host part of the *sif* driver, as it needs to check all channels manually for new messages. In the *Double Proxy* version, the driver has to poll at most one channel per process that uses SIFMP connections. For system services that may have a big number of SIFMP connections such as *chips*, this difference could become significant.

#### 4.2.1.3 Double Proxy, IPI Notifications

This version of SIFMP is very similar to the *Double Proxy* version, but instead of using Flounder channels and messages to notify applications of pending messages on SIFMP channels, it uses IPIs to notify channels of pending messages, much like UMP\_IPI does.

This results in a protocol that is largely the same as the *Double Proxy* version, but with more restrictions on the hardware. SIFMP may be faster when using IPIs, so this is a tradeoff between fewer requirements and speed.

It would probably be relatively easy to add IPIs as an optional notification mechanism to the *Double Proxy* version.

#### 4.2.1.4 Single Proxy

While the three previously discussed versions of SIFMP use a driver on both sides of the PCIe bus, this possible implementation uses only one driver part on the host.

In this version, the host driver does not only trigger one channel on the SCC with a message in the MPB and an IPI, which it does in the *Double Proxy* version, but by using that mechanism for every channel individually. The channel number for the MPB message and the core number to trigger the kernel on the right core have to be passed to the host endpoint as part of the binding process via the monitor.

The host part of the driver is still responsible for copying new messages and updating the ringbuffers, but updates to ringbuffers, i.e. new messages can only be detected when the driver checks every one of them individually, which results in a huge overhead in the form of a lot more read accesses over the PCIe bus.

#### 4.2.1.5 Encapsulation

A completely different approach is to use the Flounder channel of an application to the *sif* driver as a transport medium and encapsulate and encode SIFMP messages in other messages, e.g. LMP or UMP messages.

When sending a message, the SIFMP implementation encodes the message and sends it to the driver, along with a SIFMP channel identifier. The driver then sends the encoded message to the other part of the driver, which forwards it to the application. The SIFMP implementation at the destination decodes the message and delivers it to the application.

This idea is independent of the the notification mechanism and the number of proxies used.

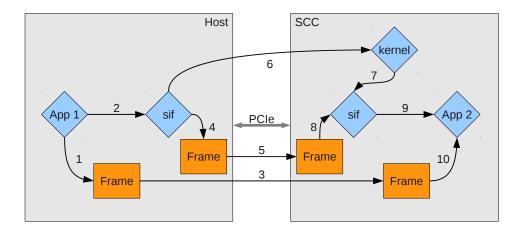

Figure 4.1: Sending of a message from host to SCC

The encapsulation of messages into SIFMP messages requires the use of a message header inside the payload to identify the channel and the arguments, which reduces the available payload space for actual arguments. But such an encapsulation scheme uses much less space than the mechanism described in the previous versions, as each application needs at most one frame for SIFMP messaging, namely for the connection to the driver.

(This version has some similarities with a routing scheme that I will describe in section 4.4.5.)

### 4.2.2 SIFMP Communication

Of the versions described previously, the *Double Proxy* implementation seemed to be the one that is most practical for a first implementation of SIFMP. For a communication protocol that crosses a PCIe bus and possibly has high round-trip times, notificationless communication and the accompanying busy waiting did not seem appropriate. The version with IPIs seemed too restrictive for this protocol. The *Single Proxy* version would have been much more complicated, because it is not as symmetric as the *Double Proxy* version, which unnecessarily complicates the library for SIFMP messaging. The *Encapsulation* strategy would have used up parts of the payload for additional headers, which I thought undesirable, especially when large amounts of data are transmitted.

With the *Double Proxy* version the SIFMP protocol is very similar to UMP\_IPI. It uses frames as ring buffers and uses a separate channel to notify the receiver of a pending message. The separate channel is an IDC connection to the *sif* driver on the host and SCC and a connection between the two driver parts.

Sending a SIFMP from host to SCC involves a number of steps (see figure 4.1):

1. The application on the host writes a message into a ringbuffer, a frame shared

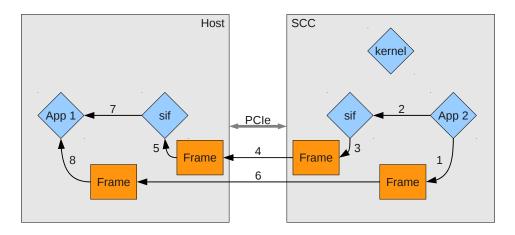

Figure 4.2: Sending of a message from SCC to host

with the host part of the *sif* driver.

- 2. The application on the host sends a notification to the *sif* driver, using any protocol available between the two processes.

- 3. The host part of the *sif* driver receives the notification and updates the ringbuffer belonging to the same channel on the SCC with the new messages.

- 4. The host part of the driver writes a notification into a ringbuffer, a frame on the host.

- 5. The host part of the driver updates a ringbuffer in a frame on the SCC, known to the SCC part of the driver, with the notification.

- 6. The host part of the driver writes a notification into the MPB of core 0 on the SCC, protected by the test-and-set lock of that core and triggers an IPI on core 0.

- 7. The kernel on core 0 sends a LMP message to *sif* to notify it of a new message on its channel to the host and to trigger the receive function of that channel.

- 8. The SCC part of the driver receives the notification from the host part ...

- 9. ... and sends a notification to the application on the SCC.

- 10. The application checks the ringbuffer and receives any pending messages on the channel.

Sending of a SIFMP message from SCC to host is different internally, but works exactly the same from an application's perspective (see figure 4.2):

- 1. The application on the SCC writes a message into a ringbuffer, a frame shared with the SCC part of the driver.

- 2. The application on the SCC sends a notification to the driver, using any protocol available.

- 3. The SCC part of the driver receives the notification from the application and writes a notification into a ring buffer, a frame in SCC memory that is known to the host part of the driver.

- 4. The host part of the *sif* driver periodically checks for new notifications in the ringbuffer from the SCC part and copies the notification to a ringbuffer in a frame on the host.

- 5. The host part of the driver receives the notification.

- 6. The driver updates the ringbuffer in the frame on the host belonging to the channel with the new message.

- 7. The host part of the driver sends a notification to the application on the host.

- 8. The application on the host receives the message from the application on the SCC.

### 4.2.3 SIF

SIFMP uses a two part driver to set up communication channels, to transmit the messages and to notify channel endpoints of new messages. The driver, called *sif*, consists of a host part, running on one of the host PC's cores and a SCC part, running on core 0 (tile 0,0) on the SCC. The host part is responsible for setting up and booting the SCC, transmitting messages, sending notifications to endpoints on the host and receiving notifications for endpoints on the SCC. The SCC part is mainly for sending notifications on its side of the PCIe bus and forwarding notifications for the host.

The two parts are connected by a manually set up SIFMP channel, which they use to coordinate and to forward notifications.

*sif* implements two interfaces, *sif* and *sif\_mgmt. sif* is the interface that most applications use. It provides the following services:

- create\_and\_register\_chan: This call creates a new SIFMP channel and registers the caller as the endpoint for future notifications on this channel. In the reply, the caller receives channel identification numbers for both endpoints and a frame that is to be used for the ringbuffer.

- get\_and\_register\_chan: With this call an application can get the frame for the ringbuffer of a SIFMP channel that was already created by the other endpoint of the channel. The caller is also registered as the endpoint for notifications on this channel.

- register\_chan: By calling register\_chan, an application can register itself as the endpoint of a channel of which it has already received the identifier and the ringbuffer frame capability, like the bootstrap monitor on the host and the monitor on core 0 on the SCC for the bootstrap channel.

- notify\_chan: This call is used by the channel endpoints to notify the driver of a new message and also by the driver to notify the endpoint.

$sif_mgmt$  is the interface that is used by the monitors to boot the SCC and set up the connection between bootstrap monitor and the monitor on core 0 on the SCC. It provides the following calls:

- map\_default\_lut: This function call causes the driver to set the LUTs entries to the default mapping (see appendix A). This call is only available on the host.

- boot\_scc: By calling this function, the bootstrap monitor can issue a complete reboot of the SCC. All the cores' configurations are reset and the cores halted. A new image is then copied to the SCC and core 0 started. This call is only available on the host.

- get\_intermon\_chan: With get\_intermon\_chan, the bootstrap monitor and the monitor on core 0 on the SCC get the channel between them. This channel is created as part of the driver's initialization procedure.

- dump\_videomem: This call dumps the contents of core 0's log memory region into a file. It is mainly used for debugging purposes.

- scc\_bind\_notification: This call is used to configure the driver and register an endpoint for the IPI that the host part of the driver sends to notify the SCC part. This call is only available on the SCC.

#### 4.2.3.1 Host Part

The host part of the driver serves as the service endpoint for applications on the host. It implements the *sif* and *sif\_mgmt* interfaces.

The host part is mainly responsible for allocating frames to be used as ringbuffers in main memory and to copy messages to and from SCC memory. Also during the boot process it is responsible for configuring the hardware and copying the binary image into SCC memory.

To check for new messages on the channel from the other part of the driver, it uses a separate thread in which the ringbuffer is monitored for new messages. If a new message was detected, the channel is triggered and the main thread can receive and handle the message.

### 4.2.3.2 SCC Part

The SCC part of the driver is mainly responsible for allocating frames to be used as ringbuffers in SCC memory. It allocates the frames from the shared memory region on memory controller 3.

Whenever a UMP\_IPI connection is created on the SCC, the originator of the connection allocates a frame of its core's shared memory. The four times 16 MB of shared memory available with the standard mapping is divided into chunks of 1 MB size. Each core can allocate frames in its 1 MB share of shared memory. With 48 cores, this leaves 16 MB of shared memory unused, which is now used by the *sif* driver for connections to the host.

### 4.2.4 Bootstrapping

Since channels between cores, their monitors and spawnd are part of the boot process, and channels between host cores and SCC cores require the *sif* driver, the driver is part of the boot process and has to be tightly integrated.

### 4.2.4.1 SIF

On the host, *sif* is started by the monitor, but is otherwise a normal process, because it is started only on request when it is needed, which is when spawnd sends a boot request. This can only happen when system services like *chips* are already available.

On the SCC however, the driver is one of the first processes to be started. When *sif* is started, there is no connection to the host yet. When Barrelfish applications are started, normally *libbarrelfish* is initialized. Part of the initialization procedure of libbarrelfish is to connect to various services like the nameservice and *serial*. With no connection to the host, this is not possible and so *sif* has to start with an uninitialized version of the library and do the initialization of needed parts like the IDC system and a connection to the memory service themselves.

#### 4.2.4.2 Monitor

Oh the SCC, the boot process is a little different from the boot process on "classical" x86 cores. Because the cores all have private physical address space, each core needs to start its own instance of a memory service. To do that, *init* is always started as if it runs on the bootstrap core, even if it doesn't. The distinction between bootstrap core and app core is made only in the *monitor*. The bootstrap core initializes the system and starts vital system services. When the SCC is started as an extension of the host, the first core to be started is neither bootstrap core nor application core. It behaves like an application core in terms of starting system services, but it does not connect to another SCC core. As the boot process is largely the same as for an application core, I decided that the first core should also be started as an application core, but with a slightly different boot procedure. I then added a flag to

the arguments that are given to the monitor on the SCC that allows it to determine whether it was started by the host and if so, choose a different initialization path.

During the boot process of an application core, the monitor requests the image of spawnd from the bootstrap monitor. Instead of transferring the whole image via messages, the bootstrap monitor sends the size and memory location of the image as a reply and the monitor on the application core can copy it to its own memory region where it should be executed. If the cores on the SCC request the image of spawnd from the bootstrap monitor, they get replies that are meaningless for them, so I had to reroute the request to a loopback function. Now the requests for spawnd images are answered by the monitor on core 0 on the SCC. The image location returned by this core is also valid on all other cores, because the same image is loaded for all cores initially.

I added a similar loopback for the UMP binding functions, because in the current version of Barrelfish, there are no checks whether UMP connections between cores are possible and the monitors would support the binding attempt using UMP. The loopback for the binding functions simply return an error to indicate that a connection with UMP is not possible and the application tries the next protocol.

#### 4.2.4.3 Inter-SIF

The connection between the two driver parts is created in a way that is very similar to the way the inter-monitor UMP channels are created. The host part of the driver, like the bootstrap monitor, passes the memory location of the frame for the ringbuffer to the kernel of the new core as a parameter. The kernel then passes the information on to the monitor, which forwards it to *sif*. The driver on the SCC then allocates the specified memory region and initializes the connection.

With UMP, this is enough to fully establish a connection, but the SIFMP connection is at this point one-sided. Messages can be sent from the SCC to the host, but not in the other direction. The driver part on the host first needs to know the channel number to send with the IPI.

The monitor on the SCC sends this channel number, together with the capability for it to the driver using the  $sif\_mgmt$  interface. The driver sends back a capability for the endpoint so the monitor can register it as the endpoint for the IPI channel. The first message that is sent between the two driver parts goes from the SCC to the host and it is part of a three-way handshake. Part of the first message is the channel number for the IPI. The messages are also used to set up the inter-monitor channel between the bootstrap monitor and the monitor on core 0 on the SCC.

When the handshake is done, the two driver parts can communicate over the PCIe bus. At this point, they export their *sif* service.

### 4.2.5 RPC Clients

When two messages in a Flounder interface belong together as call and response, they can be grouped as a remote procedure call (RPC). Flounder still generates two separate messages and they can be used separately with the same semantics as a call and a response, but Flounder is also able to generate an additional connection interface, the RPC client. RPC clients are a way to use connections conveniently in Barrelfish. RPC clients group the call and the receiving of the request together as one function for the application to call, so the application does not have to care about asynchronous messages.

RPC clients are a meta-interface to Flounder connections. They wrap existing connections and place them in their own waitset. When an application invokes a RPC function on the RPC client, the client sends the call message through the wrapped connection and waits on the waitset of the RPC client for the response. When the response is received, the RPC client can return the values sent in the response.

The extra waitset allows the RPC client to block until the response is received, without the possibility to trigger other message callbacks. This makes RPC clients much easier to use in applications where a deadlock could occur.

For SIFMP connections, the possibility to receive messages while waiting for a response is crucial, since message notifications are sent through Flounder connections. This means that the connection to *sif* must always be in the same waitset as the SIFMP connection itself. For this reason, every SIFMP connection has its own connection to *sif*, which is always placed in the same waitset as the connection.

### 4.3 Evaluation

The resources needed by a SIFMP connection can not completely be described with an absolute number, because some of the resources are used by more than one connection or even more than one application.

| nas a very sinnar concept.              |                                                              |

|-----------------------------------------|--------------------------------------------------------------|

| UMP/UMP_IPI                             | SIFMP                                                        |

| 1 frame<br>1 IPI channel (only UMP_IPI) | 2 frames (1 on the host, 1 on the SCC) 1 connection to $sif$ |

| 1 waitset entry                         | 1 waitset entry<br>1 process (driver)                        |

Nevertheless, the usage of resources can be compared to UMP/UMP\_IPI, which has a very similar concept.

#### 4.3.1 Benchmarks

I did some benchmarking of the SIFMP by using 7 testcases from the *bench/flounder\_stubs* collection of messaging benchmarks in the Barrelfish repository. All the benchmarks were completed with a 99.9% confidence interval for the mean of  $\pm 1\%$ or less. The following benchmarks were executed:

empty tests the speed of a null-message

buffer tests the speed of a 1-byte long buffer transmission

payload32\_(1,2,4,8,16) test the speed of transmitting 1, 2, 4, 8 and 16 32bit integers

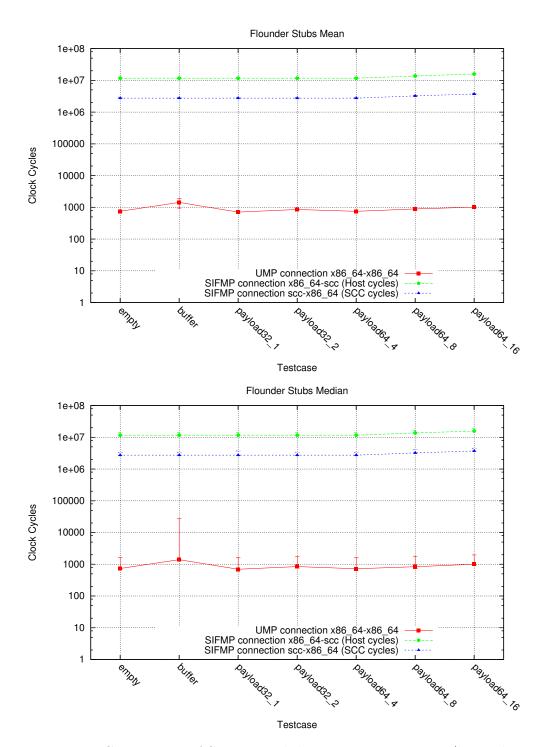

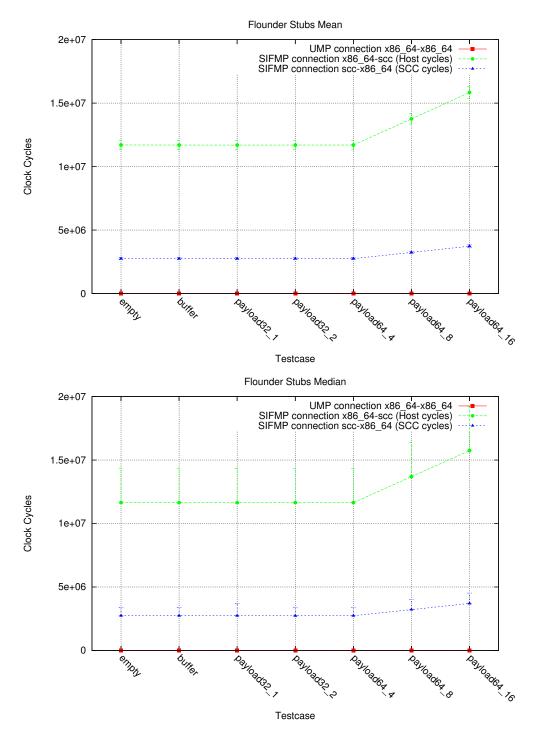

As is to be expected from a communication channel that crosses the PCIe bus, SIFMP is much slower than UMP (see figure 4.3). For SIFMP, the transmission time of a buffer is the same as the transmission time of the empty message or a message which can be transmitted in one package. With UMP, this is not the case and I can conclude that the marshalling time of SIFMP messages is a minor factor in the speed of SIFMP (see figure 4.4).

It can also be seen that the transmission time of messages that use more than one package to transmit is not proportional to the number of packages. This comes from the functioning of the buffer updating function in the driver, which becomes active after each received notification, but copies as many messages as available each time, so some messages are copied before the corresponding notification has arrived at the driver.

## 4.4 Future Work

#### 4.4.1 Multicore SCC

My version of SIFMP was only tested with a single core running on the SCC, as support for multiple cores on the SCC did not work at the time of my work.

When multiple cores should be started, great care has to be taken in creating inter-monitor connections. If further SCC-cores should be started by the host, the boot command should be forwarded to the first core on the SCC and executed there or new cores need their own endpoint of *sif*.

#### 4.4.2 Data Prefetch

The number of read accesses can be reduced by reading greater chunks of memory from the SCC. This creates a tradeoff between the number of read accesses and the time each read operation takes. The optimal size for each read access is something that has yet to be determined.

#### 4.4.3 SCC-Host messaging

Apparently, a way to actively send a message from the SCC to the host exists. The Linux-tools and -drivers provided by Intel for the SCC make use of a mailbox that appears to be a specific memory region in the SIF on the SCC. The Linux-driver writes data into it, which then apparently appears as pending message in the PCIe device visible on the host.

This mechanism could be used to reduce the number of needed read operations over the PCIe bus by changing the periodic check for new messages in SCC memory

Figure 4.3: Comparison of SIFMP with host UMP connection (logarithmic scale)

Figure 4.4: Comparison of SIFMP with host UMP connection (linear scale)

to a check for pending messages in the PCIe device or even by completely replacing the SCC-host inter-*sif* channel with the mailbox. However, this functionality is undocumented and I did not have time to test it.

### 4.4.4 IPI

Like UMP and UMP\_IPI, SIFMP could be extended by the possibility to use IPIs instead of the connection to the *sif* driver to deliver notifications.

With this, the resources needed by each SIFMP connection could be reduced, as instead of using a whole UMP\_IPI channel, only one IPI channel would be needed for a SIFMP notification connection.

Additionally, SIFMP connections might become faster when no additional connection and its unmarshalling process is involed.

### 4.4.5 Routing

SIFMP in its current state provides the possibility to connect processes on the host with processes on the SCC. If the capabilities of Barrelfish are enhanced to also span other peripheral devices like graphic cards and network cards, Barrelfish will probably need a routing infrastructure that not only allows the creation of connections with fixed protocols but also with "concatenations" of connections and protocols.

When Barrelfish is enhanced in such a way, the *sif* driver can be changed to provide routing capabilities. The driver would then become a gateway to the SCC (and to the host from the SCC).

# **5** Protocol Selection

During my work on SIFMP, I saw the need to change the way Flounder backends (protocols) are selected when a new connection is created in Barrelfish. In this chapter I will describe the problems with the old system and a first implementation of an improvement.

## 5.1 Overview

When a new connection is created in Barrelfish, the initiator of the connection has to chose the Flounder backend for this connection. In the old version of the initializer code generated by Flounder, the initiator would try each protocol in a trial and error method. The first connection attempt would be made with LMP. If that fails, it would try UMP\_IPI if available on the architecture, then UMP, BMP and SIFMP.

This works when the number of Flounder backends is small and the backends can be partially ordered with respect to their requirements and unordered pairs are mutually exclusive on any single system. This is the case with the current range of Flounder backends available.

As soon as the number of backends increases, this trial and error method may not be feasible anymore, because each backend may need to allocate resources at the beginning of the connection attempt and release them again after it has failed, a process which takes time and creates unnecessary workload for the processes guarding the resources.

Also, when connection types become more complex, such as routed connections with multiple possible gateways, a more sophisticated way of choosing the Flounder backend and its parameters is needed.

# 5.2 Implementation

My implementation of a protocol selection method introduces an additional step in the connection creation process. Before a connection attempt is made, a process sends a message to its monitor, asking for the type of connection that should be used for communication between that core and the target core.

The monitor may be the bootstrap monitor, in which case the skb is running on the same core. The monitor queries the skb for the preferred connection type and sends it back to the process.

| Backend | Requirements for connections between cores A, B            |  |

|---------|------------------------------------------------------------|--|

| LMP     | $\bullet A = B$                                            |  |

| UMP_IPI | • A, B have shared memory                                  |  |

|         | • (A, B have cache coherence for shared memory)            |  |

|         | • A can send an IPI to B                                   |  |

|         | • B can send an IPI to A                                   |  |

| UMP     | • A, B have shared memory                                  |  |

|         | • A, B have cache coherence for shared memory              |  |

| SIFMP   | • $A \neq B$                                               |  |

|         | • A, C have shared memory $(C \neq B)$                     |  |

|         | • B, D have shared memory $(D \neq C, D \neq A)$           |  |

|         | • C, D are connected by $sif$                              |  |

|         | $\bullet$ there exists a backend for the connection (A, C) |  |